# 제17회 한국반도체학술대회

The 17th Korean Conference on Semiconductors

"Semiconductor for Human and Eco"

■ 일시 2010년 2월 24일(수) ~ 26일(금)

■ 장소 호텔 인터불고 엑스코(유통단지 내), 대구

초대의 말씀

조 직

목 차

● 2010년 2월 25일(목)

Plenary Session 구두발표 포스터 발표 Chip Design Contest

◎ 2010년 2월 26일(금)

구두발표 포스터 발표

검 색

나 가 기

- 주관 경북대학교 반도체융합기술연구원, 센서기술연구소, 반도체공정교육 및 지원센터, 디스플레이 기술교육센터, 기능성소자융합플랫폼연구센터, World Class University 포항나노기술집적센터, 영남대학교 LED-IT 융합산업화연구센터, 한국반도체산업협회, 한국반도체연구조합

- 주최 한국물리학회 반도체분과회, 한국재료학회, 대한전기학회 전기재료연구회, 대한전기학회 MEMS 연구회, 대한전자공학회 반도체재료 및 부품연구회, 대한전자공학회 SoC 설계연구회, 반도체설계교육센터(IDEC)

- 후원 대구광역시, 대구컨벤션뷰로, 삼성전자, 하이닉스반도체, 한국전자통신연구원, 동부하이텍, (주)실리콘웍스, (주)피케이엘, (주)에스엔에스텍, (주)티에스이, (주)아론, (주)시스넥스, (주)울텍, (주)아이엔씨테크놀로지, (주)케이시텍, (주)루멘스, IEEE Electron Device Society Korea Chapter, IEEE SSC Seoul Chapter

# 2010년 2월 25일(목) 14:40-18:20

TP2

| Room A | Room B | Room C | Room D | Room E | Room F | EXCO        |

|--------|--------|--------|--------|--------|--------|-------------|

| 블루벨홀   | 아이리스홀  | B101   | B102   | B103   | B108   | 지하 1F Lobby |

L. Analog Design 분과

## **TP2-30**

A Low-Voltage Differential BGR with Reference Voltage Driver for High-Performance Pipelined ADC 이현중, 이상훈, 우종관, 이상윤, 임동혁, 정덕균, 김수환 서울대학교 반도체공동연구소 집적시스템설계연구실

In this paper, we present a low-voltage differential bandgap reference voltage generator to provide a stable reference for a high-performance pipelined ADC. A prototype is designed and fabricated in  $0.13\mu m$  CMOS bulk technology and operates at 1.2V nominally. It shows that the temperature coefficient of  $2.1472ppm/^{\circ}$  over a temperature range from -40° to +85°. The measured result with the supplyvoltage changes from 1.0V to 1.4V shows the supply voltage coefficient of 3mv/v. Bandgap reference core and reference voltage driver consume  $132.98~\mu W$  and 2.249~mW, and occupy  $0.071mm^{2}$  and  $0.064mm^{2}$ , respectively.

# **TP2-31**

#### DiplayPort 1.1a Standard용 2.7Gb/s 송신기의 설계

김두호, 박영석, 성창경, 김왕수, 임진수, 최우영 연세대학교 전기전자공학과

A 2.7Gb/s transmitter for DisplayPort 1.1a standard is presented. The prototype chip fabricated with Chartered 0.13 $\mu$ m process includes 20:1 serializer and pre-emphasis circuit and consumes maximum 132 mW of power from 1.2V supply voltage.

# DisplayPort 1.1a Standard용 2.7 Gb/s 송신기의 설계

# 김두호, 박영석, 성창경, 김왕수, 임진수, 최우영 연세대학교 전기전자공학과

#### 요약

A 2.7Gb/s transmitter for DisplayPort 1.1a standard is presented. The prototype chip fabricated with Chartered 0.13µm process includes 20:1 serializer and pre-emphasis circuit and consumes maximum 132 mW of power from 1.2V supply voltage.

#### 1. 서론

2006년 VESA(Video Electronics Standards Association)는 새로운 규격의 디지털 디스플레이 인터페이스인 DisplayPort를 발표하였다 [1]. DisplayPort는 각종디지털 디스플레이 장치(모니터, 디지털 TV 등)와 영상데이터를 재생하는 장치(PC, Set-top box, 위성수신기 등)를 연결하는 인터페이스 규격으로, 별도의 라이센스 사용료를 지불하지 않으므로, HDMI나 DVI와 같은 타 디지털 디스플레이 인터페이스 규격들에 비해 가격면에서 높은 경쟁력을 갖고 있다.

본 논문에서는 DisplayPort 1.1a 규격에 맞는 송신기를 설계하였다. 2장에서는 pre-emphasis회로의 설계에 대해 기술하고, 3장에서는 제작된 칩의 성능을 검증하였으며, 이 를 바탕으로 4장에서 결론을 맺었다.

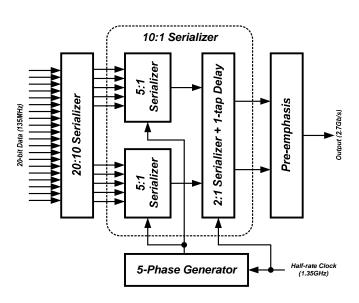

### 2. DisplayPort 1.1a용 송신기의 구현

그림 1은 설계된 송신기 회로의 구조이다. DisplayPort 에서는 10:1 Serializer를 필요로 하나, 그림에서는 20:10 Serialzier 회로가 앞에 추가되어 최종적으로는 20:1 Serialzier의 구조이다. 이는 검증시에 FPGA 보드와의 연동을 위해 FPGA 보드의 I/O 속도까지 데이터 속도를 낮춰야 하기에 불가피하게 선택된 구조이다. 뒤의 2:1 Serializer는 Pre-emphasis 회로와의 연동을 위해 1-tap delay를 추가할 수 있도록 구현되었다. 5:1 Serializer의 에서는 5개의 위상을 필요로 하므로, 외부클럭을 받아 multi-phase를 생성할 수 있도록 5-phase generator를 추가하였다.

CisplayPort 1.1a 규격에서는 1-tap의 Pre-emphasis회로를 사용하고 있으며, 본 논문에서는 [2]와 같이 1-tap 지연후에 전류의 차를 출력하는 구조를 이용하였다. Pre-emphasis회로에 사용되는 전류는 외부에서 디지털 신호를 통해 조정되며, 이를 통하여 출력의 스윙과 Pre-emphasis 정도를 바꿀 수 있다. 5:1 Serializer의 구현에는 여러 가지 방법이 있으나, 사용전력을 줄이기 위해 multi-phase를 사용하는 [3]의 구조를 사용하였다. 본 논문

에서는 [3]의 구조에서 차동 트랜지스터 밑에 전류원을 추가하여 CML형태로 동작하도록 하였다. Multi-phase를 사용하는 serializer에서는 위상이 균등하게 나오지 않는 것이 그대로 출력 지터로 나오는 문제가 있으므로, 마지막에다시 2:1 Serializer를 통해서 위상을 재정렬하여 깨끗한 출력을 내보낼 수 있도록 하였다.

#### 3. 실험

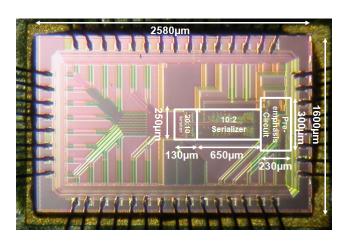

그림 2는 Chartered 0.13µm 공정을 이용하여 제작된 칩의 사진을 보이고 있다. Serialzier회로의 동작을 검증하기위해서 20-bit의 일정한 패턴(10101100111000110100)을 갖

그림 1. 설계된 송신기의 구조

그림 2. 제작된 칩의 사진

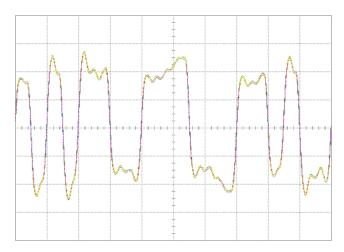

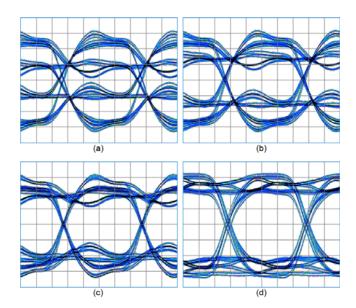

그림 3. Serializer의 동작 (2.7Gb/s, Pattern 10101100111000110100, X: 74ps/div, Y: 50mVdiff/div)

그림 4. Pre-emphasis희로의 동작 (2.7Gb/s, Pattern 1010110011100011000, X: 74ps/div, Y: 100mV/div);

- (a) 출력스윙 0.4V, Pre-emphasis 9.5 dB;

- (b) 출력스윙 0.6V, Pre-emphasis 6.0 dB;

- (c) 출력스윙 0.8V, Pre-emphasis 3.5 dB;

- (d) 출력스윙 1.2V, Pre-emphasis 0.0 dB;

는 DC 신호를 입력으로 사용하였다. 이때의 출력은 그림 3 과 같이 나타났다. 주어진 패턴에 대해서 serializer로서 동작하는 것을 확인하였다. 그림 4는 이 회로의 최대 출력 스윙이 나오는 네 가지 셋팅에 따른 2.7Gb/s에서의 출력을 나타내고 있다. 그림 상에서 나타나는 ringing은 보드의 임피던스 매칭이 잘 맞지 않아 나타난 것으로 보인다. 표1에 제작된 칩의 동작을 정리하였다.

| 사용공정         | Chartered 0.13µm Process                                |  |  |

|--------------|---------------------------------------------------------|--|--|

| 2] 0] 2] 0]. | 1.2V (SER +PE)                                          |  |  |

| 전원전압         | 3.3V (CMOS I/O)                                         |  |  |

| 동작속도         | 2.7Gbps                                                 |  |  |

| 출력신호크기       | 0.4 / $0.6$ / $0.8$ / $1.2V diff$                       |  |  |

| Pre-emphasis | 0 / 3.5 / 6 / 9.5dB                                     |  |  |

|              | $250 \times 130 \ \mu m^2 \ (20:10 \ SER)$              |  |  |

| 크기           | $250 \times 650 \ \mu \text{m}^2 \ (10.2 \ \text{SER})$ |  |  |

|              | $300 \times 230 \mu \text{m}^2 \text{ (PE)}$            |  |  |

| 소모저력         | 최대 132mW (SER+PE)                                       |  |  |

| <u> </u>     | 66mW (CMOS 3.3V I/O)                                    |  |  |

표 1. 제작된 칩의 성능

#### 4. 결론

VESA의 새로운 규격인 DisplayPort 1.1a 규격을 만족하는 송신기를 설계하였다. 설계된 회로는 20:1 serializer와 pre-emphasis 회로를 포함하고 있으며, 외부에서 공급되는 클럭을 이용하여 구동된다. 테스트 칩은 Chartered 0.13µm 공정을 이용해 제작되어 동작을 검증하였다.

#### Acknowledgements

본 연구는 지식경제부가 지원하는 국가 반도체 연구개 발사업인 "시스템집적반도체기반기술개발사업(시스템 IC 2010)"과 반도체설계교육센터(IDEC)의 지원을 받아 수행 되었습니다.

#### 참고 문헌

- Video Electronics Standards Association, "VESA DisplayPort Standard 1.1a," Jan. 11, 2008.

- Hyung-Rok Lee, Moon-Sang Hwang, Bong-Joon Lee, Young-Deok Kim, Dohwan Oh, Jaeha Kim, Sang-Hyun Lee, Deog-Kyoon Jeong, and Wonchan Kim, "A 1.2-V-Only 900-mW 10 Gb Ethernet Transceiver and XAUI Interface With Robust VCO Tuning Technique," IEEE Journal of Solid-State Circuits, Vol. 40, No. 11 pp2148-2158, Nov., 2005.

- 3. Meng-Tzer Wong and Wei-Zen Chen, "A 2.5 Gbps CMOS data serializer," Proceedings of IEEE Asia-Pacific Conference on ASIC, pp73-76, 2002.