# 2010 International Soc Design Conference

**Conference Information**

Papers

SOC

**Sponsors**

©2010 IEEE. Presonal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers or lists, or to reuse any copyrighted component of this work in other works must be obtained from the IEEE.

IEEE Catalog Number: CFP1069E-CDR ISBN: 978-1-4244-8631-1

Technical Support : Kyung Min D&P Co. Phone : 82-2-2269-1849 FAX : 82-2-2269-1846 E-mail : kim1849@korea.com

| CDC-41 Window-based image Processing Circuit                                                                    |

|-----------------------------------------------------------------------------------------------------------------|

| Min Shik Seok, Il Seuk Song, Jae Wook Jeon<br>Sungkyunkwan University, Korea41                                  |

| <b>CDC-42</b> Hardware IP design and FPGA implementation of face-detection engine for various applications      |

| Dongil Han, Jongho Choi<br>Sejong University, Korea42                                                           |

| <b>CDC-43</b> Cost-efficient implementation of a modem for scale-free uPAN systems                              |

| Soonam Yeom, Kwibeom Han and Seongjoo Lee<br>Sejong University, Korea 43                                        |

| <b>CDC-44</b> Cost-efficient implementation of an MDCM modem for 1Gbps scale-free uPAN systems                  |

| Wonsun Yoo and Seongjoo Lee<br>Sejong University, Korea44                                                       |

| CDC-45 Implementation of High Performance SoC On-Chip-Network                                                   |

| Seohoon Yang, Byongyong Kim, Chanho Lee<br>Soongsil University, Korea45                                         |

| CDC-46 1.62 and 2.7 Gb/s Dual-rate Adaptive Equalizer                                                           |

| Jinsoo Rhim, Chang-kyung Seong, Wangsoo Kim, and Woo-young Choi<br>Yonsei University, Korea46                   |

| CDC-47 Efficient Pipelined Architecture Design for H.264/AVC Main Profile Encoder                               |

| Juwon Byun, Jinha Choi, Jeyun Yu and Jaeseok Kim<br>Yonsei University, Korea47                                  |

| CDC-48 A +34dBm IIP3, 6mW Common-Drain Amplifier                                                                |

| Hong Gul Han, Sang Hoon Jung, and Tae Wook Kim<br>Yonsei University, Korea48                                    |

| CDC-49 H.264 Main Profile Decoder                                                                               |

| Jinha Choi, Juwon Byun, Youngjo Kim, and Jaeseok Kim<br>Yonsei University, Korea49                              |

| CDC-50 Low-complexity Design of PHY/MAC Modem Processor for WiMedia UWB Systems                                 |

| Sangmin Lee, Taewook Chung, Kilhwan Kim, Chulho Chung, Yongmin Jung and Jaeseok Kim<br>Yonsei University, Korea |

| <b>CDC-51</b> 6.25-Gb/s Optical Receiver Analog Front-End in a 0.13-µm CMOS Technology                          |

| Jin-Sung Youn and Woo-Young Choi<br>Yonsei University, Korea-51                                                 |

# 6.25-Gb/s Optical Receiver Analog Front-End in a 0.13-μm CMOS Technology

Jin-Sung Youn and Woo-Young Choi

Department of Electrical and Electronic Engineering, Yonsei University Seodaemun-gu, Seoul 120-749, Korea wchoi@yonsei.ac.kr

## I. INTRODUCTION

As data transmission capacity increases in many electronic interconnect applications, existing electrical interconnects face severe problems due to large channel loss, noise and power consumption. In order to solve these problems, there are active research efforts to realize high-speed optical receivers for optical interconnect applications. In this paper, we demonstrate the optical receiver front-end in a 0.13-µm CMOS technology.

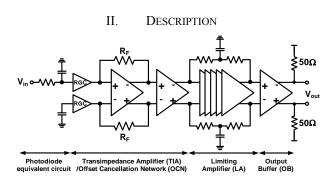

Fig. 1. Simplified architecture of the CMOS optical receiver analog front-end.

Fig. 1 shows the simplified block diagram of the fabricated CMOS optical receiver front-end. The CMOS optical receiver is composed of photodiode equivalent circuit, transimpedance amplifier (TIA), offset cancellation network (OCN), limiting amplifier (LA), and output buffer.

In photodiode equivalent circuit [1], resistor and capacitor play the role of the voltage-current converter and parasitic junction capacitance of photodiode, respectively. The TIA is composed of regulated cascode (RGC) [1], feedback amplifier having two-stage differential amplifier. The RGC can effectively isolate input parasitic capacitance. The OCN having two low-pass filters and  $f_{\rm T}$ -doubler converts the pseudodifferential signal into a fully-differential signal. The limiting amplifier consists of five-stage amplifiers and each amplifier is composed of a two-stage differential amplifier with active feedback. With the active feedback, core amplifier bandwidth can be increased beyond  $f_{\rm T}$  [2]. The output buffer is used for driving 50- $\Omega$  loads.

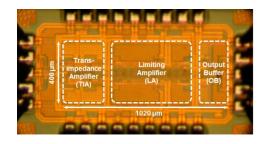

Fig. 2. Microphotograph of the fabricated CMOS optical receiver analog front-end.

Fig. 2 shows the microphotograph of the fabricated CMOS optical receiver analog front-end. The core chip size is about 1020  $\mu$ m x 400  $\mu$ m and total power consumption excluding output buffer is about 68 mW with the 1.2 V supply voltage.

### III. CHIP IMPLEMENTAION AND RESULTS

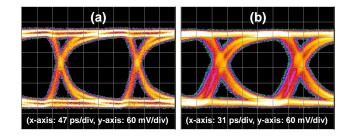

With fabricated CMOS optical receiver, data transmission measurement was conducted. The pseudorandom bit sequence (PRBS) of  $2^{31}$ -1 was generated by a pulse pattern generator (PPG) and this voltage signal was converted into current signal having about 100- $\mu$ A<sub>pp</sub> swing. Fig. 3 shows the measured eye diagrams when 4.25-Gb/s and 6.25-Gb/s data were transmitted.

Fig. 3. Measured eye-diagram of (a) 4.25-Gb/s (b) 6.25-Gb/s data when input current swing is about  $100 \ \mu A_{pp}$ .

#### REFERENCE

- S.M. Park and H.-J. Yoo, "1.25 Gb/s regulated cascode CMOS transimpedance amplifier for gigabit ethernet applications," in *IEEE Journal of Solid-State Circuits*, pp. 112-121, Jan. 2004.

- [2] S. Galal and B. Razavi, "10-Gb/s Limiting Amplifier and Laser/Modulator Driver in 0.18-μm CMOS Technology," in *IEEE Journal of Solid-State Circuits*, pp. 2138-2146, Dec. 2003.

This work (2010-0014798) was supported by Mid-career Researcher Program through NRF grant funded by the MEST. The authors are very thankful to IDEC for EDA software support as well as chip fabrication.