# 2010 International Soc Design Conference

**Conference Information**

Papers

SOC

**Sponsors**

©2010 IEEE. Presonal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers or lists, or to reuse any copyrighted component of this work in other works must be obtained from the IEEE.

IEEE Catalog Number: CFP1069E-CDR ISBN: 978-1-4244-8631-1

Technical Support : Kyung Min D&P Co. Phone : 82-2-2269-1849 FAX : 82-2-2269-1846 E-mail : kim1849@korea.com

| CDC-41 Window-based image Processing Circuit                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Min Shik Seok, Il Seuk Song, Jae Wook Jeon<br>Sungkyunkwan University, Korea·····41                                                                  |

| <b>CDC-42</b> Hardware IP design and FPGA implementation of face-detection engine for various applications                                           |

| Dongil Han, Jongho Choi<br>Sejong University, Korea42                                                                                                |

| CDC-43 Cost-efficient implementation of a modem for scale-free uPAN systems                                                                          |

| Soonam Yeom, Kwibeom Han and Seongjoo Lee<br>Sejong University, Korea43                                                                              |

| <b>CDC-44</b> Cost-efficient implementation of an MDCM modem for 1Gbps scale-free uPAN systems                                                       |

| Wonsun Yoo and Seongjoo Lee<br>Sejong University, Korea ······44                                                                                     |

| CDC-45 Implementation of High Performance SoC On-Chip-Network                                                                                        |

| Seohoon Yang, Byongyong Kim, Chanho Lee<br>Soongsil University, Korea45                                                                              |

| CDC-46 1.62 and 2.7 Gb/s Dual-rate Adaptive Equalizer<br>Jinsoo Rhim, Chang-kyung Seong, Wangsoo Kim, and Woo-young Choi<br>Yonsei University, Korea |

| CDC-47 Efficient Pipelined Architecture Design for H.264/AVC Main Profile Encoder                                                                    |

| Juwon Byun, Jinha Choi, Jeyun Yu and Jaeseok Kim<br>Yonsei University, Korea47                                                                       |

| CDC-48 A +34dBm IIP3, 6mW Common-Drain Amplifier                                                                                                     |

| Hong Gul Han, Sang Hoon Jung, and Tae Wook Kim<br>Yonsei University, Korea48                                                                         |

| CDC-49 H.264 Main Profile Decoder                                                                                                                    |

| Jinha Choi, Juwon Byun, Youngjo Kim, and Jaeseok Kim<br>Yonsei University, Korea·····49                                                              |

| CDC-50 Low-complexity Design of PHY/MAC Modem Processor for WiMedia UWB Systems                                                                      |

| Sangmin Lee, Taewook Chung, Kilhwan Kim, Chulho Chung, Yongmin Jung and Jaeseok Kim<br>Yonsei University, Korea                                      |

| CDC-51 6.25-Gb/s Optical Receiver Analog Front-End in a 0.13-µm CMOS Technology                                                                      |

| Jin-Sung Youn and Woo-Young Choi<br>Yonsei University, Korea51                                                                                       |

## 1.62 and 2.7 Gb/s Dual-rate Adaptive Equalizer

Jinsoo Rhim, Chang-kyung Seong, Wangsoo Kim, and Woo-young Choi Dept. of Electrical and Electronic Engineering Yonsei University, Seoul, Korea peter@tera.yonsei.ac.kr

### I. INTRODUCTION

Since the data rate of communication systems is limited by the channel bandwidth, various techniques have been introduced. Equalization is the most widely used solution for serial link systems in high speed communication. In this paper, an adaptive equalizer is successfully demonstrated through 15m DisplayPort cable at 1.62 Gb/s and 2.7 Gb/s.

### II. DESCRIPTION

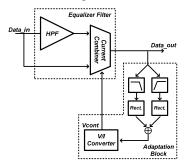

Figure. 1 shows the overall structure of our equalizer. It consists of two parts: equalizer filter which compensates the degraded high frequency components and the adaptation block which controls the amount of equalization.

Fig. 1. Block diagram of the adaptive equalizer

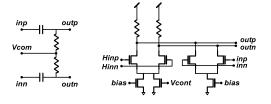

A high-pass filter with current combiner boosts up the degraded high frequency components due to the limited channel bandwidth. The current combiner is a current-mode logic (CML) buffer with two different inputs as shown in fig. 2.

Fig. 2. Schematic of (a) High-pass filter (b) Current combiner

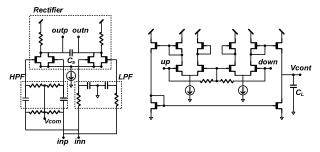

The adaptation block compares high and low frequency components of the signal after the filter and controls the current combiner for proper amount of compensation.

Fig. 4. Schematic of (a) Rectifier (b) V/I converter

#### **III. CHIP IMPLEMENTAION AND RESULTS**

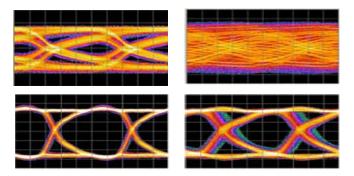

The chip is fabricated with  $0.13\mu m$  CMOS technology and occupies the area of 115  $\mu m \times 115 \mu m$  and consumes 11mW of power. Figure 4 shows the signal before and after equalizer for 1.62 Gb/s (left) and 2.7 Gb/s (right).

Table 1. Performance summary of fabricated chip

| Technology        | Chartered 0.13µm CMOS Process  |

|-------------------|--------------------------------|

| Operation Speed   | 1.62 Gb/s, 2.7 Gb/s            |

| Power consumption | 11mW (excluding output buffer) |

| Chip Area         | 115 x 115 μm <sup>2</sup>      |

Fig. 4. Eye diagram before and after equalizer

This study was supported by the IT R&D program of MKE/KEIT [KI002145, High Speed Digital Signal Processing based CMOS Circuit Design for next generation Optical Communication], and the EDA Tool was supported by IC Design Education Center (IDEC).