# 2010 International Soc Design Conference

**Conference Information**

Papers

SOC

**Sponsors**

©2010 IEEE. Presonal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers or lists, or to reuse any copyrighted component of this work in other works must be obtained from the IEEE.

IEEE Catalog Number: CFP1069E-CDR ISBN: 978-1-4244-8631-1

Technical Support : Kyung Min D&P Co. Phone : 82-2-2269-1849 FAX : 82-2-2269-1846 E-mail : kim1849@korea.com

| CDC-52 Multi-Character Processing String Matching Engine for Deep Packet<br>Inspection                                   |

|--------------------------------------------------------------------------------------------------------------------------|

| Hyejeong Hong, and Sungho Kang<br>Yonsei University, Korea52                                                             |

| CDC-53 4-Channel 3.2/6.4-Gbps Dual-rate Transmitter                                                                      |

| Duho Kim, Kwang-chun Choi, Young-seok Park, Wang-soo Kim, Jinsoo Rhim, and<br>Woo-young Choi<br>Yonsei University, Korea |

| <b>CDC-54</b> High power LED driver with current, thermal control and communication functions                            |

| Ki Soo Kwon, Yong yeon yu and Young suk Suh<br>Yeungnam University, Korea                                                |

| CDC-55 Design of a 6bit 250MS/s CMOS A/D Converter Using Input Voltage Range Detector                                    |

| Won Kim, Hak-jin Jung, Li-min Park, Tae-kyung Yoo, Kwang-sub Yoon<br>Inha University, Korea55                            |

| <b>CDC-56</b> Design of the 10bit 80MHz CMOS D/A Converter with Switching Noise Reduction Method                         |

| Jung-jin Hwang, Kwang-sub Yoon<br>Inha University, Korea56                                                               |

| <b>CDC-57</b> A CMOS Integrated Current Sensing Circuit for Wide Output Range of Boost/SEPIC DC-DC Converter             |

| Li-min Park, Hak-jin Jung, Tea-kyung Yoo, kwang-sub Yoon<br>INHA University, Korea57                                     |

| CDC-58 Design of the PWM/PFM Mode DC-DC Buck Converter with Dead-time<br>Control method                                  |

| Dong-kyun Lim, Kwang-sub Yoon<br>INHA University, Korea                                                                  |

| <b>CDC-59</b> VLSI Implementation of Pipelined QR Decomposition Processor                                                |

| S. Lee, I. Park, H. Park and S. Yu<br>Chung-Ang University, Korea                                                        |

| CDC-60 A Low-Power SRAM Using Bit-Line Charge-Recycling                                                                  |

| Si-Woo Sung, Yong-Kyu Lee, and Byung-Do Yang<br>Chungbuk National University, Korea60                                    |

| CDC-61 CMOS Inverter-Type OTA with Common-Mode Feedforward                                                               |

| Bo-Mi Noh, Eui-jin Kim, Yeong-Seuk Kim<br>Chungbuk National University, Korea61                                          |

|                                                                                                                          |

## CDC-62 Current reused Full-band UWB LNA

## 4-Channel 3.2/6.4-Gbps Dual-rate Transmitter

Duho Kim, Kwang-chun Choi, Young-seok Park, Wang-soo Kim, Jinsoo Rhim, and Woo-young Choi

Dept. of Electrical and Electronic Engineering

Yonsei University, Seoul, Korea

kimdor@tera.yonsei.ac.kr

#### I. INTRODUCTION

As the speed of A/V streaming increases, the transmissionspeed requirement of many serial links is continuously increasing. With this, providing flexibility between previous and new versions of serial links for many commercial standards becomes important. This paper demonstrates 4channel 3.2/6.4 Gbps transmitter, in which different amounts of pre-emphasis as well as output swings can be selected. The prototype chip was fabricated using  $0.13\mu$ m CMOS process.

### II. DESCRIPTION

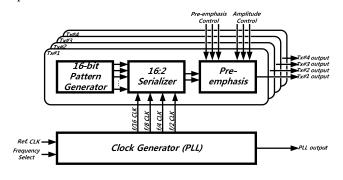

The block diagram of the transmitter is shown in Fig. 1. Each of 4 transmitters consists of parallel pattern generator, 16:2 serializer, and pre-emphasis circuit. All 4 transmitters share one PLL as a clock generator, which provides clocks having frequencies of f/16, f/8, f/4, and f/2. The desired clock frequency can be selected by an external control signal. The parallel pattern generator offers 16-bit random data having f/16 data rate. 16:2 serializer converts 16-bit data into 2-bit data using clocks of f/16, f/8, and f/4 frequencies. Pre-emphasis circuit serializes 2-bit data to 1-bit data using f/2 frequency clock, and controls the amount of output swing and pre-emphasis.

Fig. 1. Block diagram of transmitter

III. CHIP IMPLEMENTAION AND RESULTS

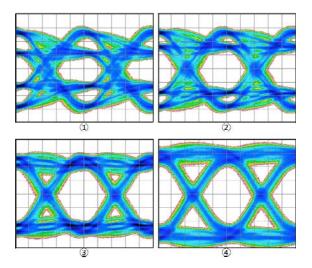

The prototype chip was fabricated using Samsung  $0.13\mu m$  CMOS process. The area of each transmitter is  $300 \times 300 \mu m^2$  and the area of PLL is  $300 \times 400 \mu m^2$ . Fabricated chip is assembled on board with COB (chip on board) packaging and consumes 600mW from 1.2V supply. PLL operates at 3.2GHz with 7.573ps<sub>rms</sub>of jitter. Fig. 2 shows measurement results of pre-emphasis and output swing control.

| Table 1. Performance of fabricated chip | Table 1 | Performance | of fabricated | chip |

|-----------------------------------------|---------|-------------|---------------|------|

|-----------------------------------------|---------|-------------|---------------|------|

| Process            | Samsung 0.13 µm CMOS                                                                                                                       |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Data Rate          | 3.2 / 6.4 Gbps                                                                                                                             |

| Supply Voltage     | 1.2 V                                                                                                                                      |

| Power Consumption  | 600mW (4ch. Tx + PLL)                                                                                                                      |

| Pre-emphasis       | 1x / 1.5x / 2x / 3x                                                                                                                        |

| Output Swing       | 200 / 300 / 400 / 600 mV <sub>diff,p2p</sub>                                                                                               |

| PLL jitter         | 7.573 ps <sub>rms</sub>                                                                                                                    |

| Area               | $300 \times 400 \ \mu\text{m}^2$ (Tx 1ch.)<br>$300 \times 300 \ \mu\text{m}^2$ (PLL)<br>$2500 \times 900 \ \mu\text{m}^2$ (including pads) |

| Transmitter Jitter | $\begin{array}{c} 31.9 \text{ ps}_{\text{p2p}} (3.2 \text{Gb/s}) \\ 44.3 \text{ ps}_{\text{p2p}} (6.4 \text{Gb/s}) \end{array}$            |

Fig. 2. Measured transmitter output; (1) pre-emphasis 3x, 200mV<sub>diff,p2p</sub> (2) pre-emphasis 2x,  $300mV_{diff,p2p}$  (3) preemphasis 1.5x,  $400mV_{diff,p2p}$  (4) without pre-emphasis  $600mV_{diff,p2p}$

This work was supported by the IT R&D program of MKE/KEIT [10034834, A development of ASIC chip for next generation high speed ATE] The authors would like to thank IC Design Education Center (IDEC) and the Korea Ministry of Knowledge Economy(MKE) for EDA software support and the fabrication of the chip.