# 2013 International SoC Design Conference

**Conference Information**

**Papers**

**Sponsors**

http://www.isocc.org

Copyright and Reprint Permission: Abstracting is permitted with credit to the source. Libraries are permitted to photocopy beyond the limit of U.S. copyright law for private use of patrons those articles inthis volume that carry a code at the bottom of the first page, provided the per-copy fee indicated in the code is paid through Copyright Clearance Center, 222 Rosewood Drive, Danvers, MA 01923. Forother copying, reprint or republication permission, write to IEEE Copyrights Manager, IEEE Operations Center, 445 Hoes Lane, Piscataway, NJ 08854. All rights reserved. Copyright ©2013 by IEEE.

IEEE Catalog Number : CFP1369E-USB ISBN : 978-1-4799-1141-7

ISOCC 2013 1의 2페이지

## **Program at a Glance**

☐ Home > Technical Program > Program at a Glance

Technical Program Download

Program Book Download

| Sunday~Monday, | November | 17~18, | 2013 |

|----------------|----------|--------|------|

|----------------|----------|--------|------|

| Tin    | ne    |                              |     | Nov. | 17                    |       |                       |                     | Mon       | day, N  | lov. 18   | 3         |       |                |

|--------|-------|------------------------------|-----|------|-----------------------|-------|-----------------------|---------------------|-----------|---------|-----------|-----------|-------|----------------|

|        | ne    |                              | DEV |      |                       |       |                       | Monday, Nov. 18     |           |         |           |           |       |                |

| From   |       | BEXCO<br>Exhibition Center 1 |     |      | BEXCO Convention Hall |       |                       |                     |           |         |           |           |       |                |

| 110111 | Till  |                              | 314 | 315  | 316                   | 317   | APEC<br>Hall<br>(205) | 201                 | 202       | 203     | 204       | 206       | 207   | Lobby          |

| 08:30  |       |                              |     |      |                       |       | Registration          |                     |           |         |           |           | •     | •              |

| 09:00  | 09:15 |                              |     |      |                       |       |                       |                     |           |         |           |           |       |                |

| 09:15  | 09:30 |                              |     |      |                       |       |                       |                     |           |         | RS-1      |           | CDC-1 | CDC            |

| 09:30  | 09:45 |                              |     |      |                       |       |                       |                     |           |         |           |           |       | Demo           |

| 09:45  | 10:00 |                              |     |      |                       |       | Break                 |                     |           |         |           |           |       | &<br>Panel /   |

| 10:00  | 10:20 |                              |     |      |                       |       |                       | Оре                 | ening     | Cerem   | ony       |           |       | IPC            |

| 10:20  | 11:10 |                              |     |      |                       |       |                       |                     | Keyno     | ote - 1 |           |           |       | Demo           |

| 11:10  | 12:00 |                              |     |      |                       |       | Keynote - 2           |                     |           |         |           |           |       |                |

| 12:00  | 13:30 |                              |     |      |                       |       |                       | Lunch               |           |         |           |           |       |                |

| 13:30  | 13:45 |                              |     |      |                       |       |                       |                     |           |         |           |           |       |                |

| 13:45  | 14:00 |                              |     |      |                       |       |                       |                     |           |         |           |           |       | CDC<br>Demo    |

| 14:00  | 14:15 |                              |     |      |                       |       |                       | COSAR               | PS-2      | SS_1    | SS-2      | DS-5      | CDC-2 | &<br>&         |

| 14:15  | 14:30 |                              |     |      |                       |       |                       | Workshop            | K3-2      | 33-1    | 33-2      | K3-3      | CDC-2 | Panel /<br>IPC |

| 14:30  | 14:45 |                              |     |      |                       |       |                       |                     |           |         |           |           |       | Demo           |

| 14:45  | 15:00 |                              |     |      |                       |       |                       |                     |           |         |           |           |       |                |

| 15:00  | 15:30 |                              |     |      |                       |       |                       |                     |           | Brea    | k         |           |       |                |

| 15:30  | 15:45 | Registration                 |     |      |                       |       |                       |                     |           |         |           |           |       |                |

| 15:45  | 16:00 |                              |     |      |                       |       |                       | COSAR               |           |         |           |           |       | CDC<br>Demo    |

| 16:00  | 16:15 |                              | T2  | Т3   | T4                    | Т5    |                       | Workshopp/<br>KORUS | RS-3 RS-4 | DS-4    | DC 4 CC 2 | SS-3 RS-6 | CDC-3 | &<br>&         |

| 16:15  | 16:30 |                              |     |      |                       |       |                       | R&D                 |           | K3-4    | 33-3      |           |       | Panel /<br>IPC |

| 16:30  | 16:45 |                              |     |      |                       |       |                       | by KETI             |           |         |           |           |       | Demo           |

| 16:45  | 17:00 |                              |     |      |                       |       |                       |                     |           |         |           |           |       |                |

| 17:00  | 17:30 |                              |     |      |                       | Break |                       |                     |           |         |           |           |       |                |

| 17:30  | 19:30 |                              |     |      |                       |       |                       |                     |           | Banqu   | et        |           |       |                |

| Session<br>No. | Session Title                                                      |

|----------------|--------------------------------------------------------------------|

| RS-1           | Design Synthesis & Analysis                                        |

| RS-2           | Emerging Technology 1                                              |

| RS-3           | Emerging Technology 2                                              |

| RS-4           | Multimedia SoC's                                                   |

| RS-5           | Analog Design Techniques                                           |

| RS-6           | DC-DC and Data converters                                          |

| SS-1           | Application Processor Technologies for Mobile                      |

| SS-2           | Mobile Multimedia Computing                                        |

| SS-3           | Effective System and Architecture for Mobile Communication Devices |

|                | Tutorial                                                           |

| T2             | High-Bandwidth Memory Interface Design?                            |

| Т3             | Energy Harvesters and Energy Processing Circuits                   |

| T4             | Circuit Design using FinFETs                                       |

Wireless Transceiver System Design for Modern Communication Standards

Tuesday, November 19, 2013

| Time  |       |                       |       | Tuse   | day, Nov | v. 19 |                     |  |  |  |

|-------|-------|-----------------------|-------|--------|----------|-------|---------------------|--|--|--|

| "     | me    | BEXCO Convention Hall |       |        |          |       |                     |  |  |  |

| From  | Till  | APEC Hall(205)        | Lobby |        |          |       |                     |  |  |  |

| 8:30  |       |                       |       |        |          |       |                     |  |  |  |

| 8:45  | 9:00  |                       |       |        |          |       |                     |  |  |  |

| 9:00  | 9:15  |                       |       |        |          |       |                     |  |  |  |

| 9:15  | 9:30  |                       | RS-7  | RS-10  | SS-5     | RS-12 |                     |  |  |  |

| 9:30  | 9:45  |                       |       |        |          |       | ETRI Demo/ Poster-1 |  |  |  |

| 9:45  | 10:00 |                       |       |        |          |       |                     |  |  |  |

| 10:00 | 10:20 |                       | Break |        |          |       |                     |  |  |  |

| 10:20 | 11:10 |                       |       |        |          |       |                     |  |  |  |

| 11:10 | 12:00 |                       | Keyno | te - 4 |          |       |                     |  |  |  |

| 12:00 | 13:30 |                       |       |        |          |       |                     |  |  |  |

| 13:30 | 13:45 |                       |       |        |          |       |                     |  |  |  |

| 13:45 | 14:00 |                       |       |        |          |       |                     |  |  |  |

| 14:00 | 14:15 |                       | RS-8  | SS-4   | SS-6     | RS-13 | ETRI Demo/ Poster-2 |  |  |  |

| 14:15 | 14:30 |                       |       |        |          |       |                     |  |  |  |

| 14:30 | 14:45 |                       |       |        |          |       |                     |  |  |  |

| 14:45 | 15:30 | Break                 |       |        |          |       |                     |  |  |  |

| 15:30 | 16:45 |                       |       |        |          |       |                     |  |  |  |

| 15:45 | 16:00 |                       | RS-9  | Rs-11  | SS-7     |       | ETDI Davis / Dash 2 |  |  |  |

| 16:00 | 16:15 |                       | K5-9  |        |          |       | ETRI Demo/ Poster-2 |  |  |  |

| 16:15 | 16:30 |                       |       |        |          |       |                     |  |  |  |

| 16:30 | 16:50 | Break                 |       |        |          |       |                     |  |  |  |

| 16:50 | 17:30 | Closing Ceremony      |       |        |          |       |                     |  |  |  |

| Session<br>No. | Session Title                                                              |

|----------------|----------------------------------------------------------------------------|

| RS-7           | Reference Circuits                                                         |

| RS-8           | Amplifiers & Biomedical SoC                                                |

| RS-9           | Clock and PLL                                                              |

| RS-10          | Communication SoC's                                                        |

| RS-11          | System IP's & Processors                                                   |

| RS-12          | SoC Testing & Verification                                                 |

| RS-13          | SoC Design Methodologies                                                   |

| SS-4           | Design Challenges in Ultra-low Power Energy Efficient Circuits and Systems |

| SS-5           | Advancements of Emerging CMOS Technologies                                 |

| SS-6           | High-Performance ASICs/IPs Design for Communication Systems                |

| SS-7           | Circuit Architectures and Methodologies for Emerging Applications          |

# 2013 International SoC Design Conference

| CDC(P)-162 | Electromagnetic Immunity Enhancement using Active Decoupling Capacitor JiSoo Hwang, NaHyun Kim, JeongMin Jo and SoYoung Kim Sungkyunkwan University, Korea 162                                   |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CDC(P)-163 | Design of Hybrid Bias Modulator for Envelope Tracking Technique Hearyun Jung, Junghyun Ham, Hyungchul Kim, Wonseob Lim, Minchul Kang and Youngoo Yang Sungkyunkwan University, Korea 163         |

| CDC(P)-164 | Design of Differential Common-Source CMOS Power Amplifier Junghyun Ham, Hyungchul Kim, Hearyun Jung, Wonseob Lim and Youngoo Yang Sungkyunkwan University, Korea 164                             |

| CDC(P)-165 | Efficiency Enhanced CMOS Power Amplifier Using Dynamic Bias Switching Circuit  Hyungchul Kim, Junghyun Ham, Jehyeon Gu and Yougoo Yang  Sungkyunkwan University, Korea 165                       |

| CDC(P)-166 | High Efficiency Transmitter and Receiver for Magnetic Resonant Wireless Power Transfer System  Jae-Hyeong Jang, Hyung-Gu Park, Ji-Hun Kang and Kang-Yoon Lee  SungKyunKwan University, Korea 166 |

| CDC(P)-167 | A 15b Second-Order Integrating ∑⊿A/D Converter  Joongho Choi  University of Seoul, Korea 167                                                                                                     |

| CDC(P)-168 | Design of PFM Boost Converter Kichang Jang, Chulkyu Park, Jihwan Kim, Ikhyun Kim, Joonho Park and Joongho Choi University of Seoul, Korea  168                                                   |

| CDC(P)-169 | All-digital Process-Variation-Calibrated Timing Generator for ATE  Kyungho Ryu, Dong-Hoon Jung and Seong-Ook Jung  Yonsei University, Korea  169                                                 |

| CDC(P)-170 | A 5-Gb/s Adaptive Equalizer & Duty-Cycle Corrector Using Asynchronous Under-Sampling Histogram Wang-Soo Kim and Woo-Young Choi Yonsei University, Korea 170                                      |

| CDC(P)-171 | A 0.4-V 88-uW 200-MHz PLL with reduced reference spurs.  Joung-Wook Moon, Kwang-Chun Choi and Woo-Young Choi  Yonsei University, Korea 171                                                       |

# **CDC Demo Session**

09:00~17:00 Lobby

Chair: Kwang Hyun Baek (Chung-Ang University, Korea) Kyoung Rok Cho (Chungbuk National University, Korea)

# A 5-Gb/s Adaptive Equalizer & Duty-Cycle Corrector Using Asynchronous Under-Sampling Histogram

Wang-Soo Kim and Woo-Young Choi

Department of Electrical and Electronic Engineering, Yonsei University Seodaemun-gu, Seoul 120-749, Korea

wchoi@yonsei.ac.kr

## I. INTRODUCTION

In the gigabit data rate single-ended I/O interconnects, intersymbol interference (ISI) and duty cycle distortion (DCD) deteriorate the deterministic jitter and bit error rate (BER) performance [1]. We present an adaptive single-ended equalizer (EQ) and duty-cycle corrector (DCC), which automatically determines the optimal equalization and duty-cycle conditions based on asynchronous under-sampling histogram [2]. It can compensates 12-dB channel loss and 25  $\sim$  75% eye crossing level. For 5-Gb/s  $2^{31}$ -1 PRBS data transmitted over 80-cm FR4 PCB trace, our single-ended EQ and DCC achieves less than  $10^{-13}$  BER and 53.2 ps peak-to-peak jitter.

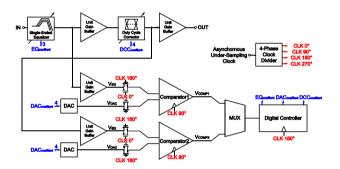

Fig. 1. Block diagram of adaptive single-ended EQ and DCC.

## II. DESCRIPTION

Fig. 1 shows the block diagram of the proposed adaptive single-ended EQ and DCC. It has a 3-bit single-ended EQ filter, a 4-bit DCC, four unit-gain buffers, a 4-phase clock divider, two 4-bit digital-to-analog converters (DACs), four track-andhold circuits, two comparators, a multiplexer, and an integrated digital controller. The first comparator extracts histograms by comparing the 5-stage single-ended EQ filter output with the reference voltage of 16-level resister ladder DAC, and the digital controller selects the optimal equalization coefficient that produces the largest peak value in histograms. The second comparator extracts histograms by comparing the 6-stage digitally controlled loading DCC output with the reference voltage, and the digital controller chooses the optimal DCC coefficient that produces the smallest gap of peak values in histograms. Unit gain buffers provide isolation from clock feed-through. Track-and-hold circuits offer sufficient timing margin for the sampling process. The multiplexer adjusts sequential operation of equalization and duty-cycle correction.

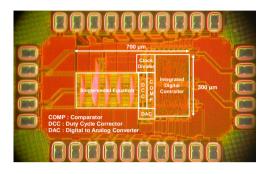

Fig. 2. Chip photograph of the adaptive single-ended EQ and DCC.

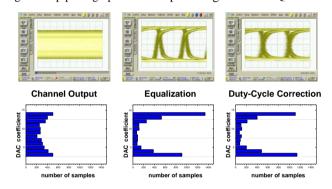

Fig. 3. Measured 5-Gb/s eye diagrams and corresponding histograms.

The clock divider generates 113-MHz quadrature clocks which are asynchronous to the date rate.

## III. CHIP IMPLEMENTAION AND MEASUREMENT RESULTS

Fig. 2 shows a chip photograph of our adaptive single-ended EQ and DCC fabricated in 0.13-μm CMOS technology. The core occupies 0.17-mm² die area. Fig. 3 shows measured eye diagrams and histograms for 80-cm FR4 PCB trace with 5-Gb/s 2<sup>31</sup>-1 PRBS data. The eye is clearly open after equalization and 50 % duty cycle is achieved after duty cycle correction. The BER is less than 10<sup>-13</sup> and the maximum peak-to-peak jitter is 53.2 ps. Total power consumption is 25 mW.

### REFERENCE

- [1] J.-D. Ihm et al., "An 80 nm 4 Gb/s/pin 32 b 512 Mb GDDR4 graphics DRAM with low-power and low-noise data-bus inversion," in *IEEE Int. Solid-State Circuits Conf. (ISSCC 2008) Dig. Tech. Papers.*

- [2] W.-S. Kim, C.-K. Seong and W.-Y. Choi, "A 5.4-Gb/s adaptive continuous-time linear equalizer using asynchronous undersampling histograms," in *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 59, no. 9, pp. 553-557, Sep. 2012.

This work [2012R1A2A1A01009233] was supported by the National Research Foundation of Korea (NRF) grant funded by the Korea government (MEST). The authors are very thankful to IC Design Education Center (IDEC) for EDA software support, and Samsung Electronics for chip fabrication.