논문 2021-58-1-3

# 25-Gbps Depletion-Type 실리콘 링 변조기 성능 극대화를 위한 소자 구조 최적화

(Device Structure Optimization for Maximizing Performance of 25-Gbps Delpletion-type Silicon-ring Modulators)

성 민 혁\*, 조 영 관\*, 김 민 규\*, 박 강 엽\*\*, 오 원 석\*\*. 최 우 영\*\*\*

(Min-Hyeok Seong, Youngkwan Jo, Minkyu Kim, Kangyeob Park, Won-Seok Oh, and Woo-Young Choi®)

요 약

본 논문은 실리콘 포토닉스 기반 depletion-type 링 변조기의 성능 최적화를 위한 소자 설계 방법을 제시하고, 이의 유효성을 실험적으로 검증한다. Depletion-type 실리콘 링 변조기의 소자 구조에 따른 동적 변조 특성 변화를 파악할 수 있는 모델을 구축하고, 이를 바탕으로 변조기의 25-Gbps eye diagram을 시뮬레이션하여 최적의 eye 성능을 갖는 소자 구조를 도출하며, 이 결과를 실험 결과와 비교한다.

#### Abstract

This paper proposes the performance optimization methodology of 25-Gbps depletion-type silicon-ring modulators, and experimentally verifies its effectiveness. A model is proposed that can describe the dependence of the dynamic modulation characteristics on the depletion-type silicon-ring modulator device structure. The model parameters that influence the ring modulator performance are identified, and their dependence on the device structure is investigated. With this, the optimal device structure that results in the best 25-Gbps eye diagrams is determined. The experimental results confirm the accuracy of our design optimization method.

Keywords: Silicon photonics, Depletion-type silicon-ring modulator, Performance optimization

## I. 서 론

실리콘 포토닉스는 다양한 응용 분야에서 높은 성능과 좋은 효율을 가지는 interconnect solution을 제공하는 광집적회로(Photonic Integrated Circuit: PIC) 구현을 가능하게 한다는 면에서 커다란 관심의 대상이 되고 있다<sup>[1~2]</sup>. 실리콘 PIC 구현에 필요한 다양한 광소자 중에서 특히 실리콘 광변조기의 성능은 광 연결 응용에

매우 중요한 위치를 차지하고 있다. 이제까지 다양한 형태의 실리콘 광변조기가 보고되었는데<sup>[3]</sup>, 실리콘 내의 carrier 양의 변화에 따른 굴절률의 변화, 즉 plasma dispersion effect를 이용하는 광변조기가 가장 많이 사용되고 있다. 다양한 실리콘 광변조기 중에서, p-n 접합에 걸린 역 바이어스 전압의 변화로 링 공진기 내부의 빛의 굴절률 변화를 유도하는 depletion-type 실리콘 링변조기(Si-RM)가 작은 소자 크기, 큰 변조 대역폭 및

Received; March 16, 2020 Revised; December 2, 2020 Accepted; December 11, 2020

<sup>\*</sup>비회원, \*\*\* 정회원, 연세대학교 전기전자공학과(Department of Electrical and Electronic Engineering, Yonsei University)

<sup>\*\*</sup> 비회원, 한국전자기술연구원(Korea Electronics Technology Institute)

<sup>©</sup> Corresponding Author(E-mail: wchoi@yonsei.ac.kr)

<sup>※</sup> 본 연구는 산업통상자원부 및 산업기술평가관리원(KEIT) 연구비 지원을 받아 수행된 연구임(과제번호: 10065666).

변조 효율을 제공하므로 활발히 연구되고 있다. 예를 들어, 인텔 연구진들은 Si-RM을 활용해서 128 Gbps급 PAM-4 광 연결용 송신기를 보고한 바 있다<sup>[4]</sup>.

고성능 Si-RM을 구현하기 위해서는 정확한 소자 모 델링과 이를 기반으로 하는 최적화 설계 방법이 필요하 다. 이에 대한 노력으로 Si-RM의 동작 특성을 coupled-mode equation으로 모델링하고 여기서 Si-RM 의 소신호 주파수 변조 특성을 도출하고 이를 바탕으로 Si-RM 변조 특성을 조사한 연구가 진행되었다<sup>[5~6]</sup>. 또 한, Si-RM의 Optical Modulation Amplitude (OMA) 와 변조 대역폭 간의 tradeoff에 대한 연구결과도 보고된 바 있다<sup>[7]</sup>. 더 나아가서. Si-RM coupled mode equation 을 수치적으로 풀어 Si-RM의 출력 eve diagram을 구 하고, 이를 실험적으로 검증한 연구결과도 있다<sup>[8]</sup>. 또한, Si-RM 소신호 변조 주파수 응답 특성과 OMA의 상관 관계를 기반으로 Si-RM의 동적 특성 최적화가 시도된 바 있다<sup>[9]</sup>. 본 연구에서는 Si-RM의 특성을 묘사하는 coupled-mode equation의 변수들이 Si-RM의 구조에 따라 어떤 영향을 받는지 시뮬레이션을 통해 분석하고, 이를 바탕으로 O-band 25 Gbps에서 가장 좋은 eye 특 성을 갖는 최적의 Si-RM 구조를 결정하였다.

본 논문은 다섯 장으로 이루어져 있다. 2장에서는 Si-RM 성능 최적화를 수행하기 위한 기본 배경과 사용된 Si-RM 모델을 설명한다. 3장에서는 최적화 설계를 위해 수행한 다양한 시뮬레이션의 과정과 결과를 설명하며, 4장에서는 이에 대한 실험적인 검증을 제시하며 시뮬레이션 결과와 실험 결과의 차이를 분석한다. 5장은 이 논문의 결론을 맺는다.

#### Ⅱ. Si-RM 모델링

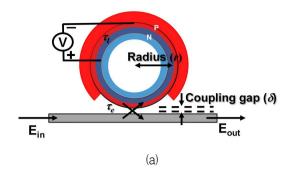

그림 1은 이 연구에서 사용된 Si-RM의 구조와 단면을 보여준다. 본 연구는 독일 IHP의 실리콘 포토닉스 파운드리를 통한 Si-RM 제작을 전제로 수행되었는데, IHP 파운드리는 그림 1(b)에서 볼 수 있듯이 2-µm buried oxide 위에 위치한 220-nm 두께의 Si 기판을 사용하며, 원 형태를 갖는 400-nm 너비의 rib 광도파로로 Si-RM을 구현한다. Si-RM 동작 특성은 아래의 coupled-mode equation으로 모델링 할 수 있다<sup>[10]</sup>.

$$\frac{d}{dt}a(t) = (j\omega - \frac{1}{\tau})a(t) - j\sqrt{\frac{2}{\tau_e}}E_{in}$$

(1)

$$E_{out} = E_{in} - j\sqrt{\frac{2}{\tau_e}} a(t)$$

(2)

그림 1. (a) 본 연구에 사용한 Si-RM의 구조, (b) 제작되는 Si-RM의 링 도파로를 자른 단면

Fig. 1. (a) The structure of Si-RM for this research, (b) Cross section of the ring waveguide of the fabricated Si-RMs.

위 식에서 a(t)는 링 공진기 내부에 저장된 에너지를 나타내며, t는 a(t)의 동적 특성 변화를 나타내는 시간상수이다. t는 링 공진기의 Q-factor와  $Q=\frac{\omega_{res}T}{2}$ 로 정의되는 관계를 가지고 있는데, 여기서  $\omega_{res}$ 는 Si-RM의 공진 각주파수이다. 또한, 시간상수 t는 두 가지 요소로 구성되어 있는데, 이는 링 내부에서의 전파 손실에 의한 a(t)의 감소를 나타내는 시간상수(t) 그리고 링 도파로와 출력 도파로의 coupling으로 인한 a(t)의 감소를 나타내는 시간상수(t)이다. t와 t0, t1 관계는 t2 가 t3 가 t4 관계는 t5 이다.

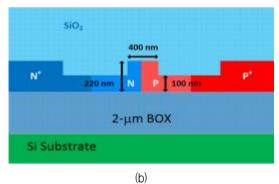

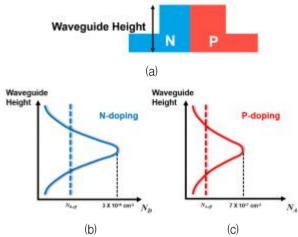

Si-RM의 성능 최적화 설계를 진행하기 전에 필요한 과정이 한 가지 존재한다. Si-RM의 동작 특성은 Si-RM의 P-영역, 그리고 N-영역의 도핑 농도 및 분포에 큰 영향을 받는데, 파운드리를 통해서 Si-RM을 제작할 경우, 이에 관한 자세한 정보는 알 수 없다. IHP 파운드리를 통해 Si-RM을 제작할 경우, nominal 피크도핑 농도(P: 7 X 10<sup>17</sup> cm<sup>-3</sup>과 N: 3 X 10<sup>18</sup> cm<sup>-3</sup>) 값들만 알 수 있기 때문에, Si-RM에 대한 정확한 시뮬레이션이 가능하지 않다. 본 연구에서는 이 문제를 극복하기 위해 그림 2의 실선으로 표현된 실제 비균일한 도핑

그림 2. (a) 링 도파로의 단면, (b) 링 도파로의 높이에 따른 n-영역 도핑 분포와 그에 따른 유효 n-영역 균일 도핑 농도( $N_{D,eff}$ ), (c) 링 도파로의 높이에 따른 p-영역 도핑 분포와 그에 따른 유효 p-영역 균일 도핑 농도( $N_{A,eff}$ )

Fig. 2. (a) Cross section of the ring waveguide, (b) N-doping profile along the waveguide height and effective uniform N-doping concentration( $N_{Deff}$ ), (c) P-doping profile along the waveguide height and effective uniform P-doping concentration( $N_{Aeff}$ ).

분포를 점선으로 표현된 균일한 유효 도핑 분포( $N_{Deff}$ 의  $N_{Aeff}$ )로 대체하여 연구를 수행하였다.  $N_{Deff}$ 의  $N_{Aeff}$  값은 제작된 Si-RM의  $\eta$ 을 측정한 후 동일한 구조의 Si-RM에 대하여 시뮬레이션을 통해 구한  $\eta$ 이 측정된  $\eta$ 과 동일한 값을 갖도록 설정하였다. 유효 도핑 농도를 정하기 위해 시간상수  $\eta$ 을 사용한 이유는  $\eta$ 이 free carrier absorption으로 인해 농도 변화에 상당히 민감하게 변하기 때문이다. 시뮬레이션은 Lumerical 사의 FDTD 그리고 MODE Solution을 이용하여 링 도파로가 갖는 전파 손실을 구한 후, 이로부터  $\eta$  값을 산출하는 방식을 사용하였다[11].

제작된 Si-RM을 이용한 실험적  $\eta$  측정은 Si-RM에 걸린 역 바이어스 전압에 따른 transmission 특성을 측정한 후, 이를 coupled-mode equation에서 구해진 아래의 Si-RM 정상 상태 transmission 특성 식에 fitting하여 수행하였다<sup>[8]</sup>.

$$\left|\frac{E_{out}}{E_{in}}\right|^2 = \left|\frac{j(\omega - \omega_{res}) + \frac{1}{\tau_l} - \frac{1}{\tau_e}}{j(\omega - \omega_{res}) + \frac{1}{\tau_l} + \frac{1}{\tau_e}}\right|^2 \tag{3}$$

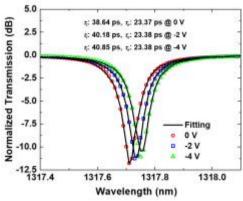

위 식에서  $\omega$ 는 입력 광의 각주파수를 나타낸다. 그림 3은  $12~\mu m$ 의 반지름(r)을 가지는 Si-RM에 대하여 다

그림 3. 12  $\mu$ m의 r을 가지는 Si-RM에 대하여 각각의 역 바이어스 전압에 따른 transmission 특성을 측정한 결과와 이를 fitting하여 추출한  $\tau$ 과  $\tau_e$

Fig. 3. Measurement results of transmission curves along various reverse bias voltages for Si-RM which has  $12-\mu m$  r and extracted  $\tau_l$  and  $\tau_e$  using fitting technique.

양한 역 바이어스 조건에서 측정된 transmission 특성 들과 식 (3)의 fitting 결과를 보여준다.

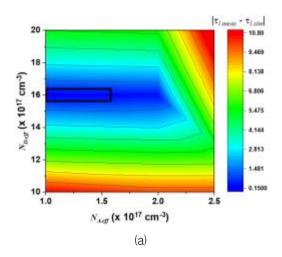

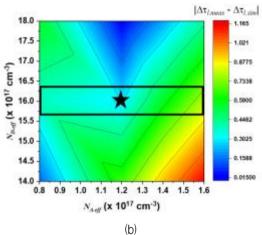

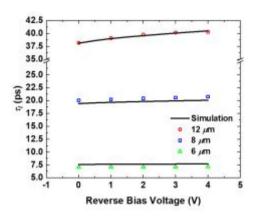

그림 4(a)는 -2 V에서 측정된  $\tau$  ( $\tau_{l.meas}$ )과 다양한  $N_{D.eff}$ ,  $N_{A.eff}$  값을 사용하여 추출한  $\tau_l$  ( $\tau_{l.sim}$ ) 간의 차이를 보여준다. 그림 4(a)에서 Box는 측정값과 시뮬레이션 값의 차이가 가장 작은 영역을 보여주며, 그림 4(b)는 이를 확대한 그림이다. 이로부터,  $N_{D.eff}=1.6$  X  $10^{18}$  cm<sup>-3</sup>,  $N_{A.eff}=1.2$  X  $10^{17}$  cm<sup>-3</sup> 일 때, 측정값과  $N_{D.eff}$ ,  $N_{A.eff}$ 을 사용한 시뮬레이션 값의 차이가 제일 작음을 알수 있다. 그림 5는 동일한 도핑 조건에서 다양한 r을 갖는 Si-RM에 대해 역 바이어스 전압을 바꾸어 가면서 보여주는  $\tau_l$ 의 측정 결과와 시뮬레이션 결과를 보여준다. 그림에서 볼 수 있듯이 이 둘은 잘 일치함을 알수 있고, 따라서 정해진  $N_{D.eff}$ ,  $N_{A.eff}$ 을 기반으로 하는 Si-RM 시뮬레이션은 제작된 Si-RM의 동작 특성을 정확히 예측하리라 기대할 수 있다.

## Ⅲ. 최적화 시뮬레이션

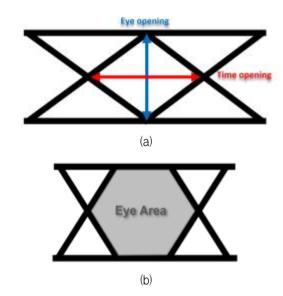

광변조기 출력 신호의 eye diagram은 그 변조기의 성능을 나타내는 가장 중요한 척도인데, 그림 6(a)가 보여주는 것처럼 eye diagram의 vertical eye opening과 lateral time opening은 각각 크면 클수록 좋다<sup>[12~13]</sup>. 동시에, 더 넓은 sampling margin을 위해서는 그림 6(b)에 색칠된 부분으로 나타내어진 eye opening area가 크면 클수록 좋다. 본 연구에서는 주어진 data rate에서

그림 4. (a) -2 V에서 측정한  $\tau_l$  ( $\tau_{l.meas}$ )과 각  $N_{D.eff}$ 와  $N_{A.eff}$ 에 따라 시뮬레이션으로 구한  $\tau_l$  ( $\tau_{l.sim}$ ) 간의 차이를 나타낸 등고선 그림, (b) Si-RM의 구동 전압(0  $V^{\sim}-4$  V)에 의한  $\tau_l$ 의 변화량의 측정값( $\Delta \tau_{l.meas}$ )과 시뮬레이션 값( $\Delta \tau_{l.sim}$ )을  $N_{D.eff}$ 와  $N_{A.eff}$ 에 따라 나타낸 등고선 그림

Fig. 4. (a) Contour map of difference between measured  $au_l$  ( $au_{l.meas}$ ) and simulated  $au_l$  ( $au_{l.sim}$ ) at -2 V along various  $N_{D.eff}$  and  $N_{A.eff}$ , (b) Contour map of difference between measured value ( $\Delta au_{l.meas}$ ) and simulated value ( $\Delta au_{l.sim}$ ) of  $au_l$  change induced by driving voltage of Si-RM (0 V~-4 V) along various  $N_{D.eff}$  and  $N_{A.eff}$ .

가장 큰 eye opening area를 갖도록 Si-RM 구조를 최 적화하려 한다.

Eye diagram 시뮬레이션은 식 (1)을 수치적으로 풀어서 수행했으며<sup>[8]</sup>, 이 결과로부터 eye opening area를 정할 수 있다. 본 연구에서는 Si-RM의 r을 6  $\mu$ m 부터 16  $\mu$ m까지 그리고 coupling gap ( $\delta$ )을 200 nm 부터 350 nm까지의 범위로 한정하였다. r이 너무 작으면 링도파로의 큰 곡률로 인해 큰 전파 손실이 발생하여  $\tau$ 이 너무 작아지기 때문에 출력 eye diagram이 충분히 크

그림 5. 각각의 r을 가지는 Si-RM에 대하여 각각의 역 바이어스 전압에 따라  $\tau$ 을 측정한 결과와 시뮬레이션을 통해 구한 결과

Fig. 5. Measurement and simulation results of  $\tau_l$  along various reverse bias voltages for Si-RMs.

그림 6. (a) Eye diagram의 한 예 그리고 이를 구성하는 eye opening과 time opening, (b) 넓은 sampling margin을 위한 eye diagram과 변조기의 성능을 알 수 있는 eye area

Fig. 6. (a) An example of eye diagram as well as eye opening and time opening which are included in eye diagram, (b) eye diagram for large sampling margin and eye area which represents performance of Si-RMs.

지 않게 되므로 너무 작은 r은 제외하였다. 또, r이 증가하면 작은 곡률로 인해 전파 손실이 감소하여  $\tau$ 은 증가하지만, r이 너무 커지면 링 도파로의 긴 둘레에 걸친 free carrier absorption의 효과로 인해 링 내부의 전파손실이 더 이상 감소하지 않게 되고  $\tau$  또한 포화 및 감소하는 경향이 존재한다. 이로 인해 일정 수준 이상의 r을 가지는 Si-RM에 대해서는 큰 성능의 변화가 발생하

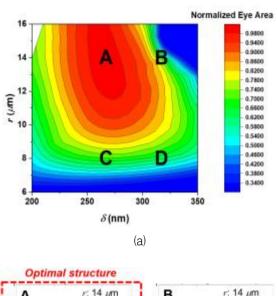

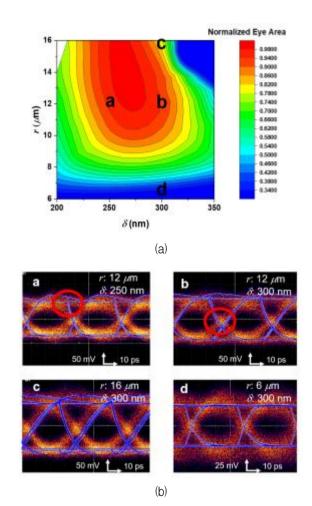

그림 8. (a) 시뮬레이션으로 구한 eye area를 정규화하여 각 r과  $\delta$ 에 따라 나타낸 등고선 그림, (b) 그림 8(a) 각 지점의 Si-RM을 시뮬레이션하여 구한 eye diagram

Fig. 8. (a) Contour map of normalized eye area along each r and  $\delta$ , (b) Simulated eye diagram at each structure in Fig. 8(a).

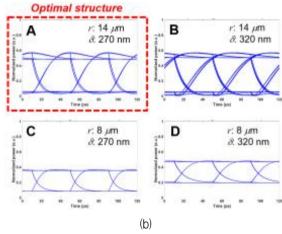

지 않으므로 r의 크기에 제한을 두었다.  $\delta$ 의 범위는 IHP 파운드리 디자인 룰에 의해 결정되는 최소의 광도 파로 간 gap 보다 크게 설정하였다. Si-RM 구동 전압 신호는 이상적인 특성을 갖는 4 V peak-to-peak (0 V  $\sim$  -4 V) PRBS7으로 정했다. Eye diagram 시뮬레이션을 위해 주어진 r과  $\delta$ 을 갖는 Si-RM의  $\tau$ 과  $\tau_e$ 를 Lumerical 사의 FDTD와 MODE Solution 시뮬레이션을 이용하여 계산하였다. 또한, 정확한 eye diagram 시뮬레이션을 위해서 구동 전압에 따른 링 도파로의 유효 굴절률( $n_{eff}$ )의 변화를 알아야하는데, 이 또한 동일한 시뮬레이션 툴을 이용하여 계산하였다. 그림 7은 다양한 경우에서 계산된  $\tau_e$ ,  $\tau_e$  그리고  $n_{eff}$  값을 보여준다. Si-RM의 특성상  $\tau_e$ 은  $\delta$ 의 영향을 받지 않으며,  $\tau_e$ 는 역

그림 7. (a) 시뮬레이션으로 구한 각각의 r에 따른  $\tau_l$ 을 역 바이어스 전압에 따라 나타낸 그림, (b) 시뮬레이션으로 구한 각각의 r과  $\delta$ 에 따른  $\tau_e$  를 나타낸 그림, (c) 시뮬레이션으로 구한 각각의 r에 따른  $n_{eff}$ 를 역 바이어스 전압에 따라 나타낸 그림

(C)

Fig. 7. (a) Simulated  $\tau_l$  at each r along various reverse bias voltages, (b) Simulated  $\tau_e$  at each r along various  $\delta$ , (c) Simulated  $n_{eff}$  at each r along various reverse bias voltages.

바이어스 전압의 영향을 크게 받지 않는다.

Si-RM의 변조 특성은 입력 광의 각주파수와 링의 공진 각주파수 간의 차이를 나타내는  $D_{\omega} = |\omega - \omega_{res}|$ 의 영향을 받는데, 본 연구에서는 OMA 값이 최대가되는  $D_{\omega} = 1/\sqrt{3} \tau$  조건을 가정하고 eye 시뮬레이션을 수행하였다<sup>[7]</sup>. 이때,  $D_{\omega}$ 를 결정짓는  $\omega_{res}$ 와  $1/\sqrt{3} \tau$ 의  $\tau$  값들은 변조 전압의 중간값인 -2 V에서의 값이다.

그림 8(a)는 시뮬레이션을 통해 구해낸 eye diagram에서 추출한 eye opening area를 r과  $\delta$ 의 변화에 대해 등고선으로 나타낸 그림이다. 그림 8(b)는 그림 8(a)의 A, B, C, D 지점에서의 eye diagram들을 보여준다. A 지점에서의 eye diagram이 다른 지점의 eye diagram에비해 가장 깔끔하고 큰 eye opening을 가지고 있다는 점을 알 수 있다. 이는 우리가 사용하는 공정에서 최적의 Si-RM은 A 지점인  $14~\mu$ m의 r 그리고 270~nm의  $\delta$ 를 가지는 Si-RM이라는 것을 의미한다.

#### Ⅳ. 시뮬레이션 결과에 대한 실험적 검증

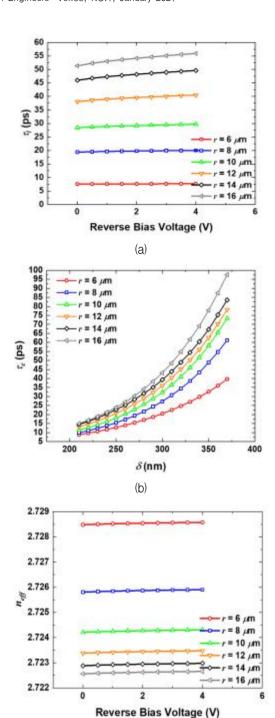

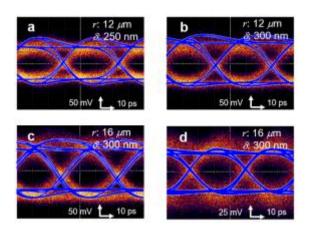

제작된 Si-RM들을 통해 최적화 시뮬레이션에 대한 실험적 검증을 실시하였다. 측정에 사용된 Si-RM 소자 는 6 µm, 12 µm, 그리고 16 µm의 r 값을 가지고 있으 며,  $6 \mu \text{m과 } 16 \mu \text{m의 } r$ 을 가지는 Si-RM은 300 nm의  $\delta$ ,  $12~\mu$ m의 r을 가지는 Si-RM은  $250~\mathrm{nm}$ 과  $300~\mathrm{nm}$ 의  $\delta$ 를 가지고 있다. 그림 9(a)의 a,b,c,d 점들은 이러한 조 건에 해당되는 Si-RM을 나타내며, 그림 9(b)는 이 조 건에서 측정된 그리고 시뮬레이션에 의한 eve diagram 을 보여준다. 여기서 주목할 점은 측정 결과와 시뮬레 이션 결과의 차이를 보여주는 빨간색 원들인데, 그 차 이는 크게 두 가지이다. 하나는 eye diagram이 각져 있 는 시뮬레이션 결과와 달리 측정 결과는 둥근 모양을 가지고 있다는 점이며, 두 번째는 시뮬레이션으로 구한 eve의 crossing point가 측정 결과와는 달리 낮다는 점 이다. 이 두 가지 차이점은 3장에서 고려하지 않았던 요인들에 의해 발생했을 가능성이 큰데, 이를 파악해야 하다.

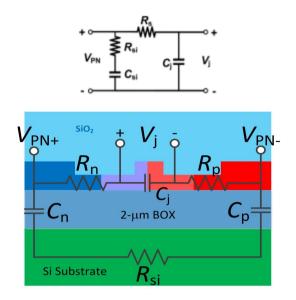

먼저 생각해 볼 수 있는 요소는 그림 10에 보이는 Si-RM 내부의 저항, p-n 접합 사이의 capacitance, 그리고 광도파로 밑에 있는 silicon substrate와 관련된 전기적 요소들이다. 여기서, 그림 10의  $R_s$ 는  $R_n$ 과  $R_p$ 를 더한 값이며  $C_s$ 는  $C_n$ || $C_p$ 이다. Si-RM의 전기적인 요소들의 구체적인 설명은 [14]에 자세히 소개되어 있다. 이러한 요소 중에서 Si-RM의 동적 변조 특성에 가장 큰 영

그림 9. (a) 그림 8(a)의 등고선 그림에 측정한 Si-RM의 지점을 표시한 그림, (b) 그림 9(a) 각 지점의 Si-RM에 대하여 시뮬레과 측정을 통해 구한 eye diagram을 겹친 그림

Fig. 9. (a) The figure which shows each point of measured Si-RMs based on figure 8(a), (b) Measured and simulated eye diagrams at each point in Fig. 8(a).

향을 주는 것은 R,와 C,로서 이들은 low pass filter의 역할을 통해 Si-RM 변조 대역폭에 영향을 준다. 하지만 이러한 회로 변수들을 표 1과 같이 실험적으로 측정한 결과 본 연구에 사용된 Si-RM에서는 이들로 인한 3-dB 변조 대역폭이 50 GHz 보다 큼을 알 수 있었고, 따라서 이는 본 연구에서 고려하고 있는 25-Gbps NRZ 변조에는 유의미한 영향을 미치지 않음을 알 수 있다. 또, C,는 Si-RM의 r에 대해 비례하며, R,는 반비례하기때문에 구조가 바뀌어도 전기적 3-dB 변조 대역폭은 25 Gbps NRZ 변조에 영향을 줄 정도로 변하지 않는다.

두 번째로는 측정 시에 사용하는 장비들의 영향이다. 측정 시 사용한 장비인 Optical Receiver (Optilab PR-23-M) 와 Oscilloscope (Tektronix CSA8000B 그

그림 10. Si-RM을 구성하는 전기적 RC 요소를 표현한 그림과 그 회로

Fig. 10. Electrical RC components which is included in Si-RMs and the circuit.

표 1. 0 V의 bias voltage에서 측정한 Rs, Cj 값과 이에 따른 전기적 3-dB 대역폭

Table1. Measured Rs, Cj at 0 V and the resulting 3-dB bandwidth.

| Radius (µm) | $R_s(\Omega)$ | $C_j$ (fF) | 3-dB bandwidth<br>(GHz) |

|-------------|---------------|------------|-------------------------|

| 6           | 409           | 4.348      | 89.498                  |

| 12          | 153           | 19.189     | 54.210                  |

| 16          | 112           | 28.127     | 50.540                  |

리고 80E03) 의 대역폭은 각각 25 GHz와 20 GHz이다. 각 장비의 data sheet이 제공하는 S21 특성을 시뮬레이션 결과에 포함시켜 eye diagram을 보정한 결과가 그림 11에 실선으로 제시되어 있다. 그림에서 볼 수 있듯이 보정된 시뮬레이션 eye diagram은 측정 결과와 비교적 잘 일치됨을 알 수 있다. 따라서 그림 8에 나온 시뮬레이션 결과를 기반으로 생각해 볼 때, IHP 파운드리를 사용하여 O-band 25-Gbps Si-RM을 구현할 때는 링 도파로의 반지름이 14  $\mu$ m, coupling gap이 270 nm 일 때, 가장 좋은 eye diagram을 얻을 수 있다고 결론지을 수 있다.

표 2는 이 논문에서 결정한 최적 구조를 가지는 Si-RM의 성능을 다른 논문의 Si-RM들과 비교하고 있다. 이 논문에서 결정한 Si-RM의 Extinction Ratio (ER) 와 OMA가 다른 논문에 있는 Si-RM들과 비교했을 때 더 크다는 사실을 알 수 있다. 이는 이 논문에서

그림 11. 그림 9(b)의 시뮬레이션으로 구한 eye diagram을 실험 장비의 S21 데이터로 보정한 후 다시 측정 결과와 겹친 그림

Fig. 11. The figure after compensating simulated eye diagrams using S21 data of experimental equipment.

표 2. 기존에 발표된 Si-RM들과의 성능 비교 Table2. Performance comparison with previously reported Si-RMs.

|                               | This<br>work | [9]  | [15] | [16] | [17] |

|-------------------------------|--------------|------|------|------|------|

| Wavelength (nm)               | 1310         | 1550 | 1550 | 1310 | 1310 |

| Peak-to-peak<br>voltage (Vpp) | 4            | 4    | 4.4  | 2.3  | 4    |

| Data rate<br>(Gbps)           | 25           | 25   | 25   | 25   | 25   |

| Ring radius (µm)              | 14           | 8    | 10   | _    | 12   |

| ER (dB)                       | 9.1          | 4.48 | 7    | 5.3  | 8    |

| Normalized<br>OMA             | 0.43         | 0.22 | -    | -    | -    |

밝힌 Si-RM의 최적화 방법이 효과가 있고, 실제 Si-RM 설계 시 이 방법을 참고하게 되면 성능이 더 좋은 Si-RM을 제작할 수 있게 됨을 방증한다.

## Ⅴ. 결 론

본 논문은 Si-RM의 성능 극대화를 위한 소자 구조 최적화 과정에 대한 연구결과를 보고했다. Si-RM의 성 능은 시간상수  $\tau_i$ 와  $\tau_i$ 에 의해 결정되는데, 소자 구조 변 화에 따른 이 시간상수들의 변화를 시뮬레이션을 통해 정하고, 이를 기반으로 하는 Si-RM eye diagram 얻어 서 가장 좋은 eye diagram을 제공하는 Si-RM 구조를 결정할 수 있었다. 최적 구조의 Si-RM이 갖는 eye diagram은 크고 깔끔한 eye를 보이고 특히 3.5 dB 이상의 ER을 가지고 있어서, 100G CWDM4 MSA 표준 스펙을 만족한다<sup>[18]</sup>.

#### REFERENCES

- [1] P. P. Absil, P. Verheyen, P. De Heyn, M. Pantouvaki, G. Lepage, J. D. Coster, and J. V. Campenhout, "Silicon photonics integrated circuits: a manufacturing platform for high density, low power optical I/O's," Opt. Express vol. 23, no. 7, pp. 9369–9378, Apr. 2015.

- [2] B. Jalali, and S. Fathpour, "Silicon Photonics," IEEE Journal of Lightwave Technology. vol. 24, no. 12, 4600–4615, Dec. 2006.

- [3] G. T. Reed, G. Mashanovich, F. Y. Gardes, and D. J. Thomson, "Silicon optical modulators," Nature Photonics, vol. 4, 518–526, Aug. 2010.

- [4] J. Sun, R. Kumar, M. Sakib, J. B. Driscoll, H. Jayatilleka, and H. Rong, "A 128 Gb/s PAM4 Silicon Microring Modulator with Integrated Thermo-Optic Resonance Tuning," IEEE Journal of Lightwave Technology, vol. 37, no. 1, pp. 110–115, Jan. 2019.

- [5] Y. Ban, J. Lee, B. Yu, S. Cho, and W. Choi, "Small-signal frequency responses for Si micro-ring modulators," IEEE Opt. Interconnects Conference, pp. 47-48. Coronado, USA, May. 2014.

- [6] S. Karimelahi and A Sheikholeslami, "Ring modulator small-signal response analysis based on pole-zero representation," Opt. Express, vol. 24, no. 7, pp. 7586-7599, Mar. 2016.

- [7] H. Yu, D. Ying, M. Pantouvaki, J. V. Campenhout, P. Absil, Y. Hao, J. Yang, and X. Jiang, "Trade-off between optical modulation amplitude and modulation bandwidth of silicon micro-ring modulators," Opt. Express, vol. 22, no. 12, pp. 15179–15189, Jun. 2014.

- [8] J. Rhim, Y. Ban, B. Yu, J. Lee, and W. Choi, "Verilog-A behavioral model for resonance-modulated silicon micro-ring modulator," Opt. Express, vol. 23, no.7, pp. 8762-8772, Mar. 2015.

- [9] Y. Kim, Y. Jo, M. kim, B. Yu, C. Mai, S. Lischke, L. Zimmermann, and W. Choi, "Parametric optimization of depletion-type Si micro-ring modulator performances," Japanese Journal of Applied Physics, vol. 58, no. 6, pp. 062006, Jun. 2019.

- [10] H. A. Haus, "Coupling of modes-resonators and

- couplers," Waves and Fields in Optoelectronics, Prentice-Hall, pp. 07632, 1984

- [11] M. Shin, Y. Ban, B. Yu, J. Rhim, L. Zimmermann and W. Choi, "Parametric Characterization of Self-Heating in Depletion-Type Si Micro-Ring Modulators," IEEE Journal of Selected Topics in Quantum Electronics, vol. 22, no. 6, pp. 3400207, Nov. 2016.

- [12] N. S. Ribeiro, E. Conforti, and C. M. Gallep, "BER Estimation from Measured Eye Diagrams of a Wavelength Regenerative Converter Employing a Single-SOA," SBMO/IEEE MTT-S International Microwave & Optoelectronics Conference, pp. 656-659, Belem, Brazil, Nov. 2009.

- [13] M. Jinno, "Effect of timing jitter on an optically controlled picosecond optical switch," Opt. Letters vol. 18, no. 17, pp. 1409–1411, Sep. 1993.

- [14] M. Shin, Y. Ban, B. Yu, M Kim, J. Rhim, L. Zimmermann, and W. Choi, "A linear equivalent circuit model for depletion-type silicon microring modulators," IEEE Transactions on Electron Devices, vol. 64, no. 3, pp. 1140-1145, Mar. 2017.

- [15] H. Li, Z. Xuan, A. Titriku, C. Li, K. Yu, B. Wang, A. Shafik, N. Qi, Y. Liu, R. Ding, T. Baehr-Jones, M. Fiorentino, M. Hochberg, S. Palermo, and P. Y. Chiang, "A 25Gb/s, 4.4 V-Swing, AC-Coupled Ring Modulator-Based WDM Transmitter with Wavelength Stabilization in 65 nm CMOS," IEEE Journal of Solid-State Circuits, vol. 50, no. 12, pp. 3145-3159, Dec. 2015.

- [16] M. Moralis-Pegios, S. Pitris, T. Alexoudi, J. Lambrecht, X. Yin, J. Bauwelinck, Y. Ban, P. de Heyn, M. Pantouvaki, J. V. Campenhout, and N. Pleros, "Chip-to-Chip Interconnect for 8-sockeet Direct Connectivity Using 25Gb/s O-band Integrated Transceiver and Routing Circuits," European Conference on Optical Communication, Roma, Italy, Sep. 2018.

- [17] M. Kim, K. Park, W. Oh, C. Mai, S. Lischke, L. Zimmermann, and W. Choi, "A 4x25-Gbps Monolithically Integrated Si Photonic WDM Transmitter with Ring Modulators," IEEE Optical Interconnects Conference, Santa Fe, USA, Apr. 2019.

- [18] 100G CWDM Spec, CWDM4-MSA.

### — 저 자 소 개 —

성 민 혁(비회원) 2019년 연세대학교 전기전자공학과 학사 졸업. 2019년 3월~현재 연세대학교 전기전자공학과 통합 과정.

조 영 관(비회원) 2017년 연세대학교 전기전자공학과 학사 졸업. 2017년 3월~현재 연세대학교 전기전자공학과 통합 과정.

<주관심분야: Silicon photonics, Optical trans ceiver>

<주관심분야: Silicon photonics, Coherent optical modulation, Si-ring modulators>

김 민 규(비회원) 2015년 연세대학교 전기전자공학과 학사 졸업. 2015년 3월~현재 연세대학교 전기전자공학과 통합 과정.

<주관심분야: Silicon photonics, Optical trans ceiver>

박 강 엽(비회원) 2006년 인천대학교 전기전자공학과 학사 졸업. 2013년 연세대학교 전기전자공학과 박사 졸업. 2013년~2015년 퍼듀대학교 EECS 2015년~현재 한국전자기술연구원

<주관심분야: Mixed-mode integrated circuits, devices, and systems for optical communication systems>

오 원 석(비회원) 1998년 인천대학교 전기전자공학과 학사 졸업. 2000년 인천대학교 전기전자공학과 석사 졸업. 2000년~현재 한국전자기술연구원

<주관심분야: Mixed-mode CMOS/Bi-CMOS integrated circuit design, High-speed wireless and wireline circuits and systems>

최 우 영(정회원) 1987년 매사추세츠공과대학(MIT) EECS, 학,석사 졸업. 1994년 매사추세츠공과대학(MIT) EECS. 박사 졸업 1994년~1995년 일본 NTT 광전자 연구소 Post-Doctoral Fellow

1995년~현재 연세대학교 전기전자공학과 교수 <주관심분야: Silicon Optical photonics, transceiver, 초고속 회로 및 시스템>