# 0.25 µm CMOS 2Gbps Pre-emphasis Circuit

이 재욱, 이 범철\*, 최 우영 연세대학교 전기전자공학과 초고속정보전송 연구실, \*전자통신연구원 스위칭팀 TEL: (02) 2123 - 7709, E-mail: patima@tera.yonsei.ac.kr

# A 0.25 µm CMOS 2Gbps Pre-emphasis Circuit

Jae-Wook Lee, Bhum-Cheol Lee\*, and Woo-Young Choi

Dept. of Electrical and Electronic Eng., Yonsei University,

\*Switching Technology Team, Electrics and Telecommunications Research Institutes

TEL: (02) 2123 - 7709, E-mail: patima@tera.yonsei.ac.kr

#### **Abstract**

To remove inter symbol interference a data transmitter is able to use FIR filter, and its simple realization is pre-emphasis circuit. This paper describes a high-speed CMOS pre-emphasis circuit and optimal operating control method and its limitations. A pre-emphasis circuit is realized with 0.25

µm CMOS technology and operates up to 2.5-Gb/s over a 1.2-meter PCB trace.

### 1. Introduction

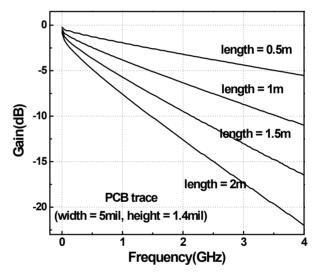

대용량의 데이터 전송에 대한 요구가 높아지면서 기존의 병렬 전송 방식을 사용할 때 소자의 I/O 수의 제한이나 채널간의 지연으로 인한 전송거리의 제한 등과 같은 많은 문제점들이 나타나고 있다. 이와 같은 문제점들을 해결하기 위해서는 기존의 병렬 전송 방식 대신 케이블을 사용한저가, 고속의 직렬 전송 방식을 사용하는 것이 시스템의 성능이나 경제적인 측면에서 유리하다. NRZ 타입의 데이터를 copper 채널을 통해 전송할 경우 신호를 손상시키는 많은 요인들이 존재한다. 그 중에서 그림 1과 같은 채널의 주파수에따른 감쇠는 ISI (Inter Symbol Interference)를일으키게 된다[1].

그림 1. Frequency-dependent signal loss

채널 특성을 극복하기 위해서 수신 단에 Equalizer를 구현하여 수신 신호의 성능을 개선하는 시도가 계속되고 있으며[2], 반면에 송신 단에 송신신호를 변조할 수 있는 회로를 구현하여 전송 신호의 성능을 개선하는 시도가 이루어지고 있다[1,3]. 송신신호를 변조하여 전송 신호의 성능을 개선시키는 방법으로 pre-emphasis 회로가 사용되고 있으며, 지연 소자를 통한 송신 데이터 조합을 통해 출력 버퍼의 신호크기를 변조하여 채널을 지난 후의 신호가 개선된 성능을 갖도록 한다.

Gbps 대역의 고속 시스템에 사용되는 preemphasis 회로는 1bit의 지연을 사용한 FIR 필터 구조가 사용되고 있으며[1,3], 본 논문에서는 이러 한 고속 pre-emphasis 회로의 설계, 구현을 통해 전송된 신호의 성능 개선을 예측하는 방법과 채 널 특성에 따른 전송 속도 및 거리의 한계를 분 석하였다.

## 2. Pre-emphasis circuit structure

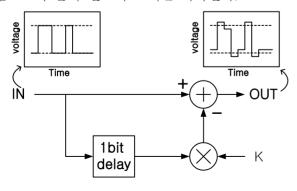

높은 주파수 대역의 신호에서 전류는 conductor의 표면을 통해서 이동하게 된다. 이러한 현상으로 인하여 전송 채널의 저항은 주파수의 함수로나타나게 되며 주파수가 높아질수록 채널의 저항이 커져서 ISI가 발생하게 된다. 이러한 채널의특성에 맞게 전송 신호를 변조할 경우 채널의 감쇠 영향에 따라 나타나는 수신 신호의 성능은 개선될 수 있다. NRZ 형태로 전송되는 신호는 두가지 상태가 존재하게 되며, 반대 상태로 천이되는 신호와 현 상태가 유지되는 신호로 나누어 생각할 수 있다. 전송신호의 고속 성분은 반대 상태로 천이 될 때 발생하게 되며, 데이터가 천이 될때 큰 크기의 신호를 발생함으로써 데이터를 변조할 수 있다. 이러한 변조된 데이터를 얻기 위해그림 2와 같은 구조를 사용하였다.

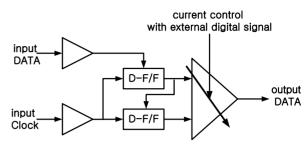

Pre-emphasis 회로는 그림 3과 같이 1bit 지연을 위한 D-F/F(D flip-flop)와 그림 4와 같은 출력 버퍼로 이루어져 있다. 데이터의 상태가 천이될 때 지연된 데이터의 반전된 값을 더함으로써 출력 신호의 크기가 커지게 되며, 상태가 유지될때 지연된 데이터에 의해 일정한 크기의 전류를 뺌으로써 출력 신호의 크기는 작아진다.

그림 2. Block diagram

그림 3. Pre-emphasis circuit

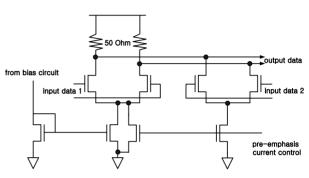

그림 4. Pre-emphasis Output buffer

출력 전압은 driving 전류와 termination 저항에 의해서 결정되며, 저항 값은 임피던스 정합을위해 50ohm이 사용된다. 채널 특성에 맞는 제어를 위하여 외부의 4가지 변조계수를 조절함으로써 pre-emphasis 전류 크기를 조절한다.

# 3. Control method and limitations of Pre-emphasis circuit

Pre-emphasis 출력버퍼에 의해 송신된 신호는 거리에 따라 다른 특성으로 나타나게 된다. 수신 단에서 깨끗한 eye diagram을 가지기 위한 변조 방법은 채널특성과 거리에 따라 변조 계수를 예 측할 수 있어야 하며, 채널 특성과 거리에 의한 한계를 알 수 있어야 한다.

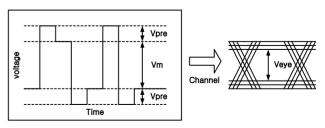

그림 5. Pre-emphasis signal

Pre-emphasis 신호를 전송할 경우 채널을 지난후 이상적인 eye diagram이 나타날 것을 예상할수 있다. 이때 송신하는 신호의 크기는 출력 버퍼의 전류 크기와 termination 저항에 의해 나타나게 되며, 전송라인의 임피던스와 정확한 정합이이루어 졌을 경우 신호크기를 예상할 수 있다.

Pre-emphasis 회로에 의해서 변조된 신호의 크기를 그림 5와 같이 Vpre, Vm에 의해 정의하였을 경우 다음 식과 같이 표현할 수 있다.

$$HDF = 1/2 \times DF = 1/4 \times DR$$

(식 2)

전송할 채널의 전달함수를 H(S)라고 한다면, 수 신 단에 나타나는 eye 크기는 다음과 같이 가정 할 수 있다.

$$Veye = Vp-p \times H(DF) = Vm \times H(HDF)$$

(식 3)

식 1과 3에 의해서 정리를 해보면 수신 단에서 최적의 eye diagram을 얻기 위해서 다음과 같은 식을 얻을 수 있다.

$$Vpre = 0.5 \times Vm \times \{H(HDF)/H(DF) - 1\}$$

(식 4)

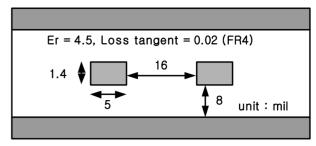

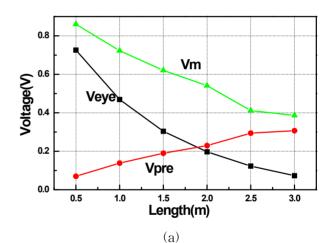

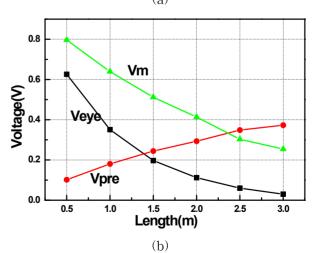

Vp-p는 출력 버퍼의 전력에 의해서 제한되며, Veye는 수신단의 sensitivity에 의해서 제한을 가지게 된다. 임피던스 값이 약 50ohm이 되도록 구성한 그림 6과 같은 HSPICE W-model을 이용하여 PCB trace에 대해서 전달함수를 구해보면 표1과 같은 채널 특성을 가짐을 알 수 있으며, 이값을 이용하여 송신단의 Vp-p값이 1V로 제한될때 수신 단에서 관찰되는 Veye를 식 3에 의해서예측할 수 있으며, Vpre 값과 Vm 값을 알 수 있으므로 Pre-emphasis 회로를 동작시킬 때 어떤면조 값을 가지는 것이 수신단의 eye diagram을 최적으로 할 수 있을지 알 수 있다. data rate 2Gbps와 3Gbps에서 예측되는 Veye와 그에 필요한 Vpre 값과 Vm 값을 그림 7에 정리하였다.

그림 6. Strip line structure and parameter 표 1. PCB trace의 Frequency transfer function

| data rate | 2Gbps  |       | 3Gbps  |       |

|-----------|--------|-------|--------|-------|

| length(m) | H(HDF) | H(DF) | H(HDF) | H(DF) |

| 0.5       | 0.844  | 0.726 | 0.786  | 0.626 |

| 1         | 0.649  | 0.469 | 0.549  | 0.351 |

| 1.5       | 0.49   | 0.304 | 0.385  | 0.197 |

| 2         | 0.364  | 0.197 | 0.271  | 0.112 |

| 2.5       | 0.299  | 0.123 | 0.198  | 0.06  |

| 3         | 0.189  | 0.073 | 0.118  | 0.03  |

그림 7. 채널 길이에 따른 수신 신호의 eye 크기와 변조신호의 전압; (a)2Gbps일때, (b)3Gbps일때

그림 7에서 볼 수 있듯이 출력버퍼의 최대 전압이 1V로 제한받을 때 수신 단의 sensitivity가 0.1V라면 2Gbps의 데이터를 송신할 때 2.5m 이상의 거리에서는 정확한 데이터 수신이 불가능함임을 예상할 수 있으며, 3Gbps의 데이터일 경우 2m이상의 거리에서는 수신 단이 데이터를 정확히 복원할 수 없음을 예상할 수 있다. 분석된 데이터는 최적의 Pre-emphasis를 이용하여 데이터를 송신하고, 채널특성에 따른 ISI를 제외한 noise가 없을 경우를 가정한 것이므로 실제 회로의 잡음 환경에서는 이보다 더 좋지 않은 성능이 예상된다.

#### 4. Measurement Results

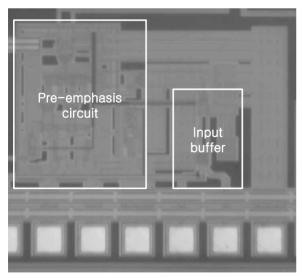

그림 8은 제작된 Pre-emphasis 회로의 칩 사진으로 면적은 약 500/m×500/m이다. 측정을 위하여같은 칩 내부에 제작된 PLL(Phase Locked Loops)에 의해서 클록을 제공받으며, 외부에서 입력되는 데이터를 Pre-emphasis 회로를 통해서 출력하도록 되어 있다.

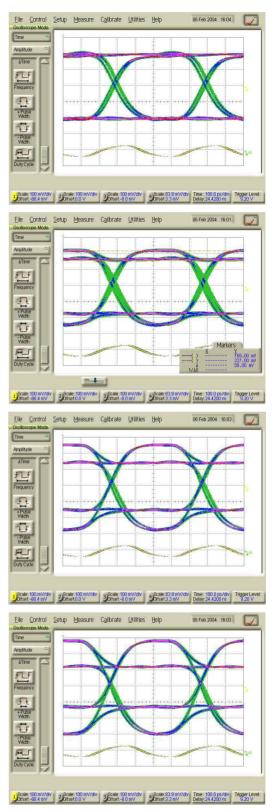

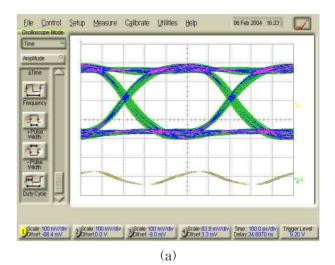

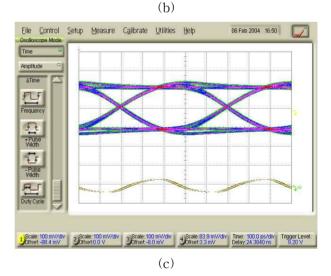

그림 9는 설계된 Pre-emphasis 회로를 2Gbps에서 동작시켰을 때 나타난 측정결과이다. 4가지변조 방식이 있으며, 각각 pre-emphasis 전류를넣지 않았을 경우와 2.5mA, 5mA, 7.5mA의 전류를 사용하였을 경우 전송라인을 통과 시키지 않았을 때 나타난 파형이다.

그림 8. Chip photograph

그림 9. Pre-emphasis Buffer Output signal @2Gbps; 위에서부터 0mA, 2.5mA, 5mA, 7.5mA 의 Pre-emphasis 전류를 사용하였을 경우. Scales are 100mV/div and 100ps/div.

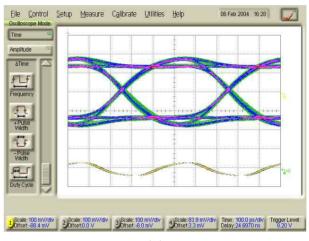

제작된 Pre-emphasis 회로의 성능을 검증하기 위하여 2Gbps 대역에서 30cm, 60cm, 120cm의 PCB trace를 사용하여, 각 전송 거리에 따른 각각의 Pre-emphasis 출력파형을 측정하였다. 거리가 길어질수록 변조 값을 키워야 깨끗한 eye diagram을 얻을 수 있었으며, 그림 10에서 각 경우의 eye diagram을 나타내었다. 제작된 회로의 출력은 pre-emphasis 동작을 하지 않을 경우 16mA를 구동하여 400mV의 출력 값을 갖도록 설계되어 있으며, pre-emphasis 동작을 할 경우 더 많은 전류를 흘리게 된다.

각각의 경우에 대한 eye diagram을 살펴보면 채널의 감쇠에 의해서 수신 단에 나타나는 eye의 크기가 작아졌지만 깨끗하게 나타나는 것을 알수 있으며, 거리에 따른 pre-emphasis 계수를 좀더 세분화하여 제어할 경우 보다 개선된 eye를 얻을 수 있을 것이다. coaxial cable 경우 frequency dependent loss가 PCB trace 보다는 작게 일어나지만 그 종류에 따라서 길이가 약 4-5배 증가할 때 같은 현상이 일어나며, 주파수 응답을 알 수 있을 경우에 PCB trace와 같이 전송 신호의 eye opening을 예측할 수 있다.

그림 10 (c)의 경우 예측된 값과의 비교를 해 보면, 전송된 채널의 길이는 실험에 사용된 PCB trace 외에 측정을 위해 장비와 연결된 케이블과 칩 측정용 PCB board의 패턴이 추가되었으며, 추 가된 채널 길이를 약 20cm로 생각하여 전송채널 의 길이를 140cm로 생각할 수 있다 또, 3장에서 분석한 2Gbps에서의 1.4m 전송 시 발생하는 eye 값 0.35와 출력 버퍼의 7.5mA 변조 시 출력 전압 이 그림 9의 (d)의 0.6V이므로, 출력 eve의 크기 는 약 200mV로 예측가능하다. 이것은 그림 10의 (c)의 eve 가 약 200mV로 나타나므로 예측된 결 과와 일치함을 알 수 있다. 분석된 값은 채널의 ISI 만을 감안한 것으로 추가의 noise에 의해 성 능이 악화될 수 있으며, 사용되는 칩의 패키지, 전송 채널의 임피던스 부정합 등에 의해서 더욱 악화될 수 있을 것으로 생각된다.

그림 10. Eye diagram @2Gbps; (a) PCB trace length 30cm에서 pre-emphasis current 2.5mA 사용하였을 경우, (b) 60cm에서 5mA 사용하였을 경우, (c) 120cm에서 7.5mA 사용하였을 경우. Scales are 100mV/div and 100ps/div.

### 5. Conclusion

본 논문에서는 고속 데이터 전송 시 채널에서 발생하는 ISI에 의해 생기는 신호의 왜곡을 개선 하기 위해 사용되는 Pre-emphasis 회로를  $0.25\mu$ m CMOS 공정을 사용하여 설계하였으며, 측정을 통 해 그 동작을 검증하였다.

또, 전송 속도 및 전송 거리에 따라 다르게 나타나는 채널의 특성에 알맞은 Pre-emphasis 회로의 제어 방법을 제시하였으며, 수식화하여 분석하였다. 제작된 회로의 2Gbps 대역에서의 측정값을통해 예측된 값과 일치함을 알 수 있었으며, 수신단의 sensitivity에 의한 Pre-emphasis 회로에 따른 전송거리의 한계를 알 수 있을 것이다.

#### Reference

- [1] W. J. Dally and J. Poulton, "Transmitter equalization for 4-Gbps signaling," *IEEE Micro*, vol. 17, pp. 48-56, Jan.-Feb. 1997.

- [2] Yoshiharu Kudoh et. al., "A 0.13um CMOS 5-Gb/s 10-meter 28AWG Cable Transceiver with No-Feedback-Loop Continuous-Time Post-Equalizer," *IEEE J. Solid-State Circuits*, vol. 38, pp. 741-746, May. 2003.

- [3] M. Bruensteiner, et. al., "3.3-V CMOS Pre-Equalization VCSEL Transmitter for Gigabit Multimode Fiber Links," *IEEE Photonics Technology Letters*, vol. 11, pp. 1301–1303, Oct. 1999.