# ZigBee용 CMOS RF 송신기 구현

# 권재관 오원석° 최우영 연세대학교 전기전자공학과, KETI SOC연구센터°

e-mail: jkwon@yonsei.ac.kr

# Implementation of a CMOS RF Transmitter for ZigBee Applications

Jae-Kwan Kwon, Won-Seok Oho Woo-Young Choi Dept. of Electrical and Electronics Eng., Yonsei Univ., SOC Research Center, KETI°

### **Abstract**

Wireless Personal Area Networks(WPAN, IEEE 802.15.3) 응용을 위해 저전압, 저전력으로 구동되는 915MHz 0.18Om CMOS 전송단(transmitter)를 구현하 였다. 전송단은 PGA(programable gain amplifier), 상 향 믹서(up-mixer), 구동 증폭기(Driver-amp)로 이루 어진다. 상향 믹서는 트렌스컨덕턴스 단을 이용하여 주파수 변환이득을 조정이 가능하며, 구동 증폭기에서 도 출력 전력을 조절 할 수 있게 설계하였다. 제작된 전송단은 16dB의 전압 이득을 갖고 이득의 변화폭은 46dB이며, 최대 출력은 OdBm이다. 전체 전류소모는 1.8V 공급전압에서 30mA이다.

## I. 서론

IEEE802.15.4(Wireless Personal Area Network: WPAN) 의 규격에 바탕을 둔 ZigBee는 상대적으로 짧은 전송거리에서의 정보전송 시스템이다. WPAN은 네트워크 구성요소들간의 근거리 이동 통신이기 때문 에 구조가 간단하고 전력 소모가 작으며 구현 비용이 낮아야 한다. ZigBee 특징은 설치의 간편성, 근거리 동작, 매우 낮은 생산 단가 그리고 오래 사용할 만한 배터리 수명에 있다[1]. 이런 요구를 만족시키는 시 스템을 구현하기 위해 CMOS공정을 이용한 회로 구현

이 관심이 대상이 된다. 전송단 시스템은 low-IF 방 식을 사용하여 주파수가 바로 기저 대역(Base-Band) 으로 떨어지기 때문에 슈퍼헤테로다인 방식과 비교하 여 더 높은 집적화를 할 수 있으며 시스템이 간단해지 고 저 전력으로 구현 할 수 있게 된다. [2] [3]

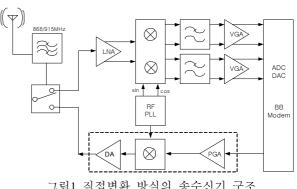

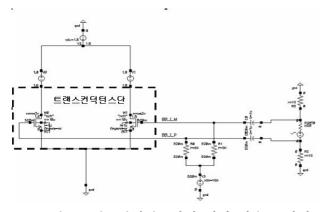

그림1 직접변환 방식의 송수신기 구조

[그림 1]이 설계된 전송 단의 전체 블록이다. 전송단 은 전체적으로 세 부분으로 나눌 수 있다. 우선, DAC (Digital to Analog Converter)에서 나온 기저대역 (Base Band)신호를 상향믹서에 적절한 입력 동작범위 로 만들어 주는 PGA가 있고, 기저대역 주파수의 신호를 원하는 RF주파수 신호로 만들어주는 상향믹서와 무선으로 방사하기 위한 출력 전력을 만들어주는 구동 증폭기가 있다. 그리고 채널 선택을 위한 주파수를 만들어 내는 부분인 주파수 합성단 (frequency synthesizer)으로 나눌 수 있다. 주파수 합성단은 테스트를 위해 외부에서 신호 발생기(signal generator)를 통해 인가하는 방법을 사용 하였다.

## II. RF 송신기 설계

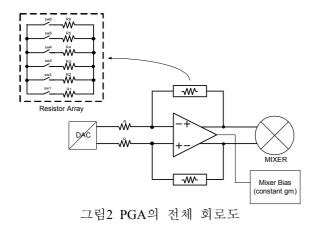

PGA (programable gain amplifier)는 Digital

### 2.1 PGA설계

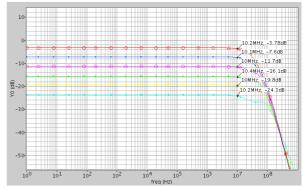

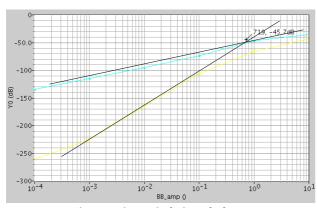

Analog Converter (DAC)와 상향 믹서(up-mixer) 사이에 위치 한다. [그림 2]는 PGA의 회로도를 나타낸 것이다. 이PGA는 전송단 전체에서 가장 큰 이득 조절 범위를 가지며 그에 따라 시스템 전체의 동작 범위 (dynamic range)를 조절 할 수 있게 설계 하였다. 다음 단인 상향 믹서와 구동증폭기가 선형 이득을 갖는 범위에서 동작하기 위한 입력 레벨을 결정해 주는 것이 PGA의 역할이다. PGA는10MHz의 주파수 응답특성을 가지며 여섯 개의 디지털 컨트롤 이득단을 가지고 있다. 이득변환에 따른 각 저항 값을 [표1]에 나타내었다. [그림3]은 각 저항 값에 변화에 따라PGA의 AC 응답의 변화를 나타낸 것이다. 각 단계마다 4dB의이득 변화가 생기게 저항 값을 결정해 주었고 그 범위는 -4dB에서 -24dB이다. DAC와 믹서 사이에 AC coupling을 하기 위해 PGA의 출력 동상모드 전압은

믹서의 바이어스 전압을 인가하였다. 그래서 믹서의

바이어스 회로는 PGA의 동상모드 출력전압을 인가해

서 믹서와 PGA간 DC-오프셋을 해결 하였다.

그림3 PGA 의 저항 조절에 따른 AC응답곡선

#### 班1. PGA Gain and Resister Value

| Gain setting | Gain(dB) | Resister Value |

|--------------|----------|----------------|

| G1           | -3.7dB   | 15k            |

| G2           | -4.6dB   | 13k            |

| G3           | -11.7dB  | 10k            |

| G4           | -16.1dB  | 7k             |

| G5           | -19.1dB  | 4k             |

| G6           | -24.3dB  | 1k             |

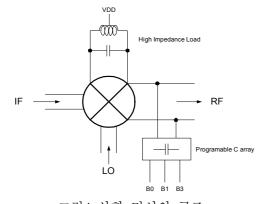

### 2.2 상향믹서 설계

길버트 셀 믹서는 일반적으로 믹서나 곱셈 기에서 이용 된다. 이 구조의 특징은 노이즈 특성, 선형성, 각 포트간 격리(isolation)가 좋고 주파수 응답이 높고 전류 재사용(current reuse)이 가능하다는 것이다. [3] 믹서 전체의 변환 이득은 (식1)과 같이 나타낼 수 있다.

$$G = g_m \cdot 2\pi \cdot Z_{out} \tag{1}$$

여기서 은 부하 임피던스를 나타낸다. 출력 저항을 높이기 위한 방법으로 LC tank를 믹서의 부하로 구현했다. [그림4] 조절 가능한 커패시터 배열(programable capacitor array)을 디지털적으로 조절 할 수 있게 하여 제작 시 나타날 수 있는 변수로 인해 부하 임피던스가 변화하는 것을 보상 시킬 수 있다.

이 믹서의 코어는 트랜스 컨덕턴스단, 스위칭단, 그리고 부하단으로 나눌 수 있다. 스위칭단이 스위치로 이용 된다면 전체 믹서의 선형성은 트랜스 컨덕턴스단에 의해 결정된다. 믹서의 비선형 성분들은 MOS 트랜지스터의 square-law특성에 기반 한다. [6] 이런 트랜스컨덕턴스단의 비선형 성분 때문에 입력레벨 범위가 제한된다.

그림4 상향 믹서의 구조

그림5 트랜스컨덕턴스단의 선형 성을 구하기 위한 테스트 회로도

그림6. 트랜스 컨덕턴스단의 IP3

그래서 -45dB의 signal distortion ratio(SDR)을 만족하는 트랜스 컨덕턴스단을 설계 하고자 하였다. [그림 5] PGA에서 나올 수 있는 신호의 최대값(718mV)에서 -46dB의 signal distortion ratio(SDR)을 얻었다. [그림 6] 이와 같은 방법으로 PGA의 입력 DC출력 레벨에서 신호의 선형 성이 보장되고 충분한 변환 이득을 갖는 트랜스컨덕턴스단이 구현 되었다. [7]

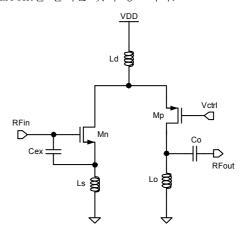

## 2.3 구동증폭기(Driver Amplifier) 설계

높은 전력을 전송하기 위해, 구동앰프는 높은 이득과 선형성을 가져야 한다. 구동 앰프는 folded-cascode 구조를 이용하여 설계하였다. [4] [그림7] Folded-cascode 구조는 아래의 이유로 선택 하였다. 우선, folded-cascode 구조는 voltage headroom이 크다. 그래서 선형 성이 더 향상 될 수 있다. 또한 PMOS(Mp)의 DC 전류를 Vctrl로 변화시키면 이득이조절이 가능하다. 주어진 드레인 전류에 대해 최대 전력 효율을 내기 위한 동작모드에서 드레인 전류()의식을 식(2)에 나타내었다. [8]

$$I_{D} = i_{d,peak} = \frac{f_{t} \sqrt{2P_{in}}}{f_{0} \sqrt{R_{s}}}$$

(2)

저 전력으로 동작하는 전송단을 위해서는 식(2)에서 ID current를 줄이는 것이 중요하다.

그림7 설계된 Driver Amp

$P_{in}$  은 동작 조건에서 상수이고  $R_s$ 는 일반적으로 구동 앰프의 앞 단에 의해서 결정 된다. 그래서  $f_t$ 를 줄이는 것이 저전력으로 동작하는데 중요한 부분이 된다. PMOS는 NMOS에 비해  $f_t$ 가 훨씬 낮기 때문에 구동증폭기의 입력 단에서 사용 되었다. 그리고 저 전력 동작의 다른 방법으로 외부 커패시터 Cex를 추가하는 것이다.

이 방법으로  $f_{\text{max}}$ 를 줄이는 결과를 가져올 수 있다. 이러한 방법을 이용하여 ID전류를 줄일 수 있다. Lo, Co는 출력 매칭(output matching)을 위해 사용했고 Ld는 RF choke, Ls는 source degeneration inductor이다.

# III. 측정결과

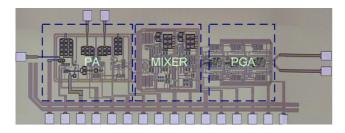

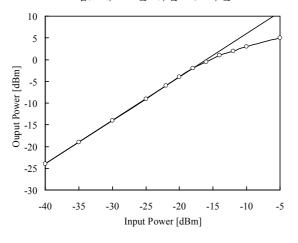

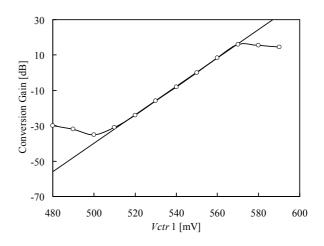

전체 칩 사진은 [그림8]이고 [그림9]는 테스트 PCB를 제작한 그림이다. 전체 칩에 대한 P-1dB는 0dBm으로 측정되어 설계의 요구조건에 만족하는 결과를 볼 수 있다. [그림 10] 선형적인 전력이득의 변화를 구동 증폭기의 이득 변화요소(Vctrl)를 통해 측정한 것을 [그림11]에 나타내었다.

그림8 제작된 송신 단 칩 사진

그림9 테스트를 위한 PCB사진

그림10전체 전송 단의 측정된 P-1dB

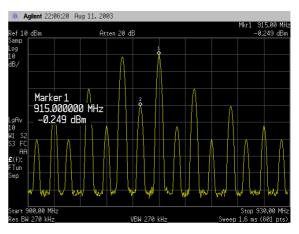

구동 증폭기의 이득 조절에 따라 약 40dB의 선형적인 전력 변환 이득의 범위가 생기는 것을 확인 할 수 있 었다. 최종 출력에 대한 스펙트럼을 [그림12]에 나타내 었다. 성능 측정에 대한 최종 결과를 [표1]에 정리 하 였다.

그림11 구동증폭기의 Vctrl의 변화에 따른 송신 단 전력 변환 이득의 변화

그림12 최종 출력 스펙트럼

# III. 결론

ZigBee 어플리케이션을 위해 저전력으로 동작 하면서 변환 이득을 조절 할 수 있는 송신단을 제작하였다. 상향믹서는 트렌스컨덕턴스 단의 사용으로 선형적인 믹서의 변환 이득을 낼 수 있고구동 증폭기는 외부 커패시터와 Vctrl을 이용하여 원하는 전류 소모에서 원하는 출력 전력을 만족 할 수 있다. 측정 결과는 16dB의 변환 이득에 46dB의 변환 이득 범위를 가지면서 0dBm의 최대 출력 전력을 가진다. 구현된 송신단은3x2mm의 면적을 가지며, 1.8V의 공급 전압으로 32mA의 전류를 소모한다. 전체 결과를 [표2]에 정리하였다.

## 표2 전체 전송 단 측정 결과

| Operating frequency  | 915MHz       |

|----------------------|--------------|

| OIP3                 | 10dBm        |

| Output P-1dB point   | 0dBm         |

| conversion gain      | 16dB         |

| Gain-range variation | 46dB         |

| Die Size             | 3.5 x 2.3 mm |

| Technology           | 0.18um CMOS  |

| supply voltage       | 1.8V         |

| Current              | 32mA         |

# 참고 문헌

- [1] Jose A. Gutierrez, and E. H. Callaway, Low-Rate Wireless Personal Area Networks, IEEE Press 2004. [2] A.A. Abidi. "Direct Conversion Radio Transceiver for Digital Communications". IEEE Journal of Solid-State Circuits, vol.30, pp.1399-1410, December 1995.

- [3] B. Razavi, "Design Considerations for Direct Conversion Receivers", IEEE Transactions on Circuits and Systems-II: Analog and digital Signal Processing, vol.44, no.6, pg428-435, June 1997.

- [4] Behzad Razavi, "RF microelectronics," 2000,

- [5] Hung-Che Wei, Ro-Min Weng and Kun-Yi Lin, "A 1.5V high-linearity CMOS mixer for 2.4GHz Application", ISCAS, I-561, 2004

- [6] B. Gilbert, "The Multi-tanh principle: a tutorial overview," IEEE Journal of Solid State Circuits, vol. 33, no. 1, pp.2-17, Jan.2001

- [7] C. C. Chang,R.M.Weng,J.C.Huang, K. Hsu and K. Y..Lin, "A 1.5V high gain CMOS MIXER for 2.4-GHz applications," IEEE International Symposium on Circuits and Systems, vol.2,pp.782-785, May 2001.

[6] T. K. K. Tsang, and M.N. El-Gamal, "Gain Controllable Very Low Voltage (<1V) 8-9GHz Integrated CMOS LNA's," Radio Frequency Integrated Circuits(RFIC) Symposium, pp. 205-208,

2002.